产品 | 网联摄像头模块LAN电缆供电用隔离型DC-DC转换器:小型化、低噪声、符合IEEE802.3af标准

村田制作所进一步扩大了面向PoE的隔离型DC-DC转换器产品阵容,推出了符合IEEE802.3af标准的PD(Powered Device,PoE系统中接受电力的设备)用隔离型DC-DC转换器。村田已开始本产品的量产,并可提供样品。 近年来,在安全摄像头、生物识别设备等网联设备中开始利用PoE技术实现LAN电缆供电。PoE,Power over Ethernet,利用LAN电缆构建网络的同时进行供电,这不仅提高了安装的灵活性,还能实现成本降低。 在此背景下,适合PoE兼容设备的小型电源模块的需求持续增长。特别是生物识别设备通常需要约10瓦的电力供应,而IEEE802.3af标准支持最大15瓦的供电,因而非常适合该类设备。 因此,村田开发了符合IEEE802.3af标准的本产品。该产品采用26×0.58×0.27英寸的小型低矮设计,提高了电路板布局的灵活性。该产品主要适用于对空间节省和低噪声特性有要求的摄像头模块和生物识别设备,同时也为其他通信设备的小型化做出贡献。 主要规格 符合IEEE802.3af各Class的隔离型DC-DC转换器模块 小型且低背(26×0.58×0.27英寸,即26×14.8×6.8mm),增加布局灵活性 宽广的工作温度范围(-40°C至+85°C),适用于多种应用 村田PoE用隔离型DC-DC转换器 MYBSP系列目前有四个型号,均已量产并可提供样品。各型号重要参数规格如下列表格: 规格参数 MYBSP00502ABFB MYBSP00502ABFS MYBSP00502ABFT MYBSP00502ABFU 该新品主要应用范围为IEEE802.3af兼容设备,包括无线接入点、生物识别设备、安全摄像头、摄像头模块、IP电话、音频扬声器等等。

DC-DC转换器

Murata村田中国 . 2025-09-24 690

市场 | 全球智能手机平均售价将从2025年的370美元升至2029年的412美元

全球智能手机平均售价预计将从2025年的370美元(约合人民币2,700元)稳步升至2029年的412美元(约合人民币3,000元),年均复合增长率(CAGR)达3%,在经历近期波动后逐步恢复至常态。 全球智能手机年收入预计到2029年将达到5640亿美元(约合人民币4万亿),2025年至2029年的CAGR为5%。 GenAI的加速落地、关税波动的缓和以及各区域市场结构的演变,共同支撑ASP在2029年前保持正向走势。 尽管2025年下半年出货量预计放缓,但北美市场的ASP预计仍将同比增长7%;而中国市场ASP预计同比增长3.6%,主要由高端机型推动。 苹果仍然是高端手机ASP的支柱,受发达市场对Pro机型的需求以及新兴市场出货量增长带动,预计其平均售价将从2025年的919美元升至2029年的近1000美元。 在高端化趋势的推动下,全球智能手机市场的ASP持续逐年增长。根据Counterpoint Research《市场展望追踪报告》,全球智能手机市场的ASP预计将从2024年的357美元升至2025年的370美元,并在2029年达到412美元,CAGR为3%。除了高端化趋势带来的提升外,5G的普及和消费者对高级功能的偏好(即便在中端机型中也是如此)也推动了这一稳步增长。 展望2025年第二季度,市场表现比预期更趋正常。Counterpoint Research最新预测显示,2025年全球智能手机出货量将同比增长2.5%,高于第一季度预测的1.9%,但低于年初预计的4%。出货放缓的原因包括价格上涨、供应链调整和宏观经济压力。2025年ASP预计同比增长3.5%至370美元,高于此前预测的2.3%,主要受北美ASP上涨,以及印度和亚太其他地区经济复苏带动的价格回升推动。随着ASP增速快于出货量,这两方面的综合提升将推动智能手机收入在2025年同比增长近6%。从长远来看,预计这一势头将推动2025至2029年的收入保持5%的CAGR,从而在2029年年收入达到5640亿美元。 全球智能手机市场ASP预测,2022-2029 图:ASP基于批发价格(来源:Counterpoint《市场展望 — ASP预测追踪报告》) 从疫情期间的需求波动到供应链挑战,再到近期关税引发的市场波动,经过多年动荡后全球智能手机市场正逐步恢复常态。美国运营商的持续大力促销使得库存并未积压,手机品牌厂商也维持着其常规的的发布周期和采购策略。Counterpoint的市场展望预计2025年下半年至2026年市场将更为“常态化”,进一步印证了我们对平均售价增长和稳定销量将维持收入增长的预测。迄今为止,智能手机基本未受到美国对贸易伙伴加征关税的影响,相比汽车、半导体和其他消费电子领域更具韧性。然而,美国关税的不确定性以及低迷的宏观经济环境,仍可能在未来使形势更加复杂。 受到上半年提前出货影响,北美出货量预计将在2025年下半年下滑,但关税传导将推动全年ASP同比增长7%。苹果的高端机型、运营商的持续促销以及折叠屏产品的亮眼表现预计将使ASP在2026年升至984美元。从长远来看,美国将在维持全球ASP高位方面发挥稳定作用,但由于其本身已是一个高端市场,故在2029年前将会对ASP提供更加渐进式的贡献。我们预计因贸易环境不会再度引发价格的突然上涨,因为新增成本将被供应商、分销商和消费者共同消化。 在中国,2025年第二季度预测显示ASP走势较第一季度小幅回落。基于最新数据跟踪,Counterpoint将2025年全年ASP同比增速由此前的4%下调至3.6%。结构性抬升主要由华为、OPPO与vivo推动。苹果方面,预计2025年在华ASP同比提升约2%;尽管出货略有下滑,但受Pro机型占比上升带动,整体表现优于我们在Q1时的下行预期。展望长期,中国市场的高端化趋势将继续抬升全球ASP,并强化其在全球高端智能手机市场中的影响力。 印度将继续支持中端市场,其2025年ASP仍将保持在250美元以下,但随着高端化趋势演进,预计其价格将逐渐上涨,到2029年达到287美元。功能机用户向智能机迁移、城乡及农村地区需求上升以及数字化普及增长将为中端与高端机型带来稳定的发展动力。 苹果仍然是高端市场的支柱,受其Pro和基本机型(包括最新的"e "和"Air "系列)组合的推动,预计其平均售价将从2025年的919美元上升到2029年的近1000美元。iPhone 16e导致2025年Q1的ASP同比下降9%,但随着下半年Pro机型的普及,预计ASP将有所改善。苹果正有意采取双重战略:在出货量方面,苹果正在扩大其消费者基础,通过e与Air系列进军新兴市场及消费领域;而在ASP方面,苹果正通过Pro机型巩固其高端主导地位,同时为2026年首款折叠屏产品的推出做好准备。长远来看(2026-2029年),美国、中国和欧洲仍将是苹果的核心市场,而拉美、中东非和印度等价格敏感市场将主要依靠iPhone基础款和旧款机型带动出货增长。 全球主要智能手机品牌ASP预测及CAGR,2025-2029 图:Counterpoint《市场展望 — ASP预测追踪报告》 三星的ASP走势预计将保持稳定。2025年上半年,该品牌旗舰机型的表现将拉低其全年ASP,但折叠屏手机和GenAI的集成将支撑其未来的长期增长。另一方面,三星在新兴市场的中端细分市场中所占比重较大,这将限制其ASP的增长潜力。小米、OPPO、vivo等其他安卓厂商也在推行高端化战略,但由于中国市场需求低迷以及印度市场表现平平,导致2025年的ASP增长相对温和。 华为在回归后正强化其在中国本土市场的ASP增长。随着自研芯片供应链限制的缓解,华为的Mate和Pura系列正在推动其ASP走高。同时折叠屏手机的强势表现也进一步支持了 ASP的增长。HarmonyOS的用户忠诚度为高端定价增添了优势,我们看好华为在海外市场的扩张潜力。 在2024-2025年期间,GenAI智能手机的出现导致每台设备的物料清单(BoM)成本增加约40-60美元,在该类型手机面世的开始抬高了价格。随着AI逐渐成熟,ASP增长将从“成本推动”转向“价值驱动”,因为消费者会更愿意为围绕AI功能为核心的设备支付溢价。 虽然折叠屏智能手机目前在全球出货量中所占比例仍不到2%,但其ASP正在不断走高,并进一步影响着消费者对高端产品的看法。预计苹果将在2026年底推出折叠屏手机,或将带来ASP的新一轮提升,并重塑行业折叠屏手机基准。 综合来看,全球智能手机ASP预测比较乐观。目前,关税波动的影响正在减弱,同时供应链趋于稳定,而高端智能手机的普及、GenAI和折叠屏创新也将共同推动ASP温和上行。这种增长将是常态化而非爆炸性的,因而尽管存在宏观不利因素,ASP仍将稳步攀升。

智能手机

Counterpoint 咨询 . 2025-09-24 1640

企业 | 安谋科技Arm China与览山电子签署Arm Total Access授权许可协议,合力满足智能汽车全场景“芯”需求

安谋科技(中国)有限公司(以下简称“安谋科技”)与技术领先的车规级MCU及电源芯片供应商重庆览山汽车电子有限公司(以下简称“览山电子”)共同宣布,双方签署了一项为期多年的Arm® Total Access技术授权订阅许可协议。此次合作将进一步深化双方在车载MCU等关键领域的协作,合力满足智能汽车全场景“芯”需求,为汽车产业智能化提速注入“芯”动力。 安谋科技销售及业务发展负责人赵永超表示:“Arm架构作为当前主流的车载计算芯片架构,已成为国内外众多汽车电子厂商的首选。览山电子作为国内车规级芯片领域的创新先锋,自2022年成立以来便与安谋科技紧密协作,其基于Arm架构的高性能、高安全、高可靠车规芯片已成功导入多家头部主机厂,实现整车全场景覆盖。览山电子选择Arm Total Access方案,标志着双方合作进入全方位深化新阶段,期待围绕智能汽车全场景芯片开展更深度的创新协同。” 览山电子总经理李涛表示:“借力Arm全球领先的技术生态,览山电子构建了覆盖智能汽车全场景的车规MCU产品矩阵,这得益于安谋科技的深度支持。Arm Total Access方案与公司未来产品规划高度契合,我们可以通过‘一次订阅,多次使用’的方式,使用Arm最新技术、工具和服务支持,并能实现多个研发项目的并行推进,这将助力我们整合资源、加速技术创新与产品上市,向‘国内领先、世界一流汽车半导体企业’的愿景迈进。” Arm Total Access赋能高效创“芯”,赢得智能汽车市场先机 智能电动汽车时代,车用MCU迎来“量质齐升”的变革:一方面,MCU应用扩展至车身、动力、底盘、智舱、智驾全场景,需求规模显著增长;另一方面,汽车电子电气架构升级与AI技术渗透,推动车用MCU从“功能实现”转向“智能协同”,这使得市场对车用MCU在高性能、高实时性、高安全性方面的要求愈发严苛,而这些性能指标也成为衡量车用MCU核心竞争力的关键标准。 这一趋势给芯片企业带来市场机遇的同时也带来技术、开发、商务、成本等多方面挑战。作为全球应用最广泛的计算平台,Arm技术凭借高能效比、成熟生态、灵活扩展的优势,迄今已赋能全球超过3100亿颗芯片,是全球车用MCU的主流选择。尤其对于览山电子这类有清晰研发与商业规划的成熟企业而言,Arm Total Access方案能充分契合企业基于Arm前沿、多元技术快速研发市场引领性产品的创新需求。 Arm Total Access是“Arm技术授权订阅”模式的重要选项,可为企业提供一站式技术支持:整合最新Arm IP资源、工具、技术培训及软件服务,支持多项目并行研发,简化商务流程,并保障研发自由度与效率。Arm Total Access 和 Arm Flexible Access 自2024年正式落地国内以来便赢得了客户的广泛认可,目前共计已有超70家国内客户选择了上述两种授权订阅模式。 借力主流Arm技术生态,构建全场景车用MCU产品矩阵 借力Arm全球领先的技术生态,览山电子在三年内构建了全栈自主研发的车规MCU产品组合及配套电源芯片,覆盖高、中、低端应用场景,契合不同汽车电子电气架构,全面满足智能汽车全场景需求。 • 高端旗舰LS-N636产品:搭载3核Arm Cortex®-R52,采用先进车规eFlash工艺,满足ASIL-D最高安全等级,应用于动力域控、智能底盘等核心领域,代表国产域控MCU领先水平。 • 性能先锋LS-E3X系列:采用Cortex-M7内核,单核至四核全覆盖,多IO口、多封装形式,可覆盖多种车身控制应用。 • 中端主力LS-E14X系列:基于Cortex-M4F内核,配备高性能独立HSM模块,支持硬件非对称加密,应对严苛信息安全法规。 • 经济优选LS-E10X系列:依托Cortex-M0+内核,在功能安全、通信模块等方面灵活创新,适配多类车身电子场景。 当前,览山电子系列产品推进顺利。LS-E14X系列已在多个头部客户量产装车,LS-N636、LS-E3X与LS-E10X即将正式量产,后续览山电子还在持续研发基于Arm Cortex-R52、Cortex-M内核的多系列车用MCU新品,在高端产品研发上聚焦发力,着重满足未来5-10年域控新需求。 未来,安谋科技与览山电子将持续深化在产品研发、技术创新及生态构建等方面的合作,携手推动智能汽车技术创新与产业升级。 Arm Total Access是“Arm技术授权订阅”模式中的一种方案选项。通过便捷的一站式订阅,该方案为企业提供最全面的Arm技术及各类IP资源、工具与模型、支持与培训服务,以及丰富的软件资源,特别适用于需采用最前沿的Arm技术和多种Arm产品构建复杂系统的成熟企业。Arm Total Access方案使企业能够根据自身业务需求和规划,灵活地使用并探索Arm IP解决方案组合,以同时推进多个重点项目,同时最大限度减少繁琐的商业谈判流程,实现一站式加速各类芯片设计。如需了解更多详细,请点击此链接。

MCU

Arm . 2025-09-24 760

企业 | 安森美获得奥拉半导体Vcore电源技术,强化其在人工智能数据中心领域的领先地位

中国上海 - 2025年9月 24日--安森美(onsemi,美国纳斯达克股票代号:ON) 宣布已与奥拉半导体(Aura Semiconductor)达成协议,获得其Vcore电源技术及相关知识产权(IP)许可。此项战略交易将增强安森美的电源管理产品组合与路线图,加速实现公司在人工智能(AI)数据中心应用中覆盖从电网到核心的完整电源系统的愿景。 “此次交易彰显了我们致力于通过提供全方位差异化的智能电源解决方案,满足未来AI数据中心的能源与效率需求的承诺。”安森美智能感知及模拟与混合信号事业部总裁Sudhir Gopalswamy表示,“将这些技术整合到我们更广泛的电源管理产品组合中,将使我们能够提供具备更高功率密度、效率和散热性能的解决方案,从而提升单机架的算力。” 安森美在硅及碳化硅(SiC)技术领域拥有数十年的创新积累,为固态变压器、电源、800 V直流配电以及核心供电等应用提供行业领先的解决方案。通过整合这些技术,安森美将成为少数几家能够以可扩展、实用的设计,满足现代AI基础设施严苛电力需求的公司之一。 安森美预计,此次交易在完成后的首个财年对其按美国通用会计准则(GAAP)和非GAAP计算的每股收益影响甚微,此后将有所增加。该交易预计将于2025年第四季度完成,但需满足惯例成交条件。上述对协议及收购的描述并非详尽无遗,具体内容以安森美向美国证券交易委员会(“SEC”)提交的8-K报表中披露的相关信息为准。

AI

onsemi . 2025-09-24 1050

MDD系列MOS,提升新国标电动自行车充电效率与安全性

一、背景与政策驱动 部分电动自行车用户长期面临充电安全隐患,根源在于充电器产品缺乏强制认证标准,导致大量劣质配件通过非正规渠道流入市场,引发充电起火、电池爆炸等安全事故。为应对这一行业痛点,市场监管总局于2024年7月2日发布新规,明确自2025年11月起,电动自行车充电器及锂电池组必须通过3C认证并标注认证标志后方可出厂销售,推动行业向正规化、标准化方向发展。 二、各类充电器认证情况概览 截至2025年7月31日,在电动自行车新国标充电器类型中,锂电充电器占比51%,实际过认证数量为86个,铅酸充电器占比48%,实际数量为82个,钠电充电器占比均为1%,实际数量为2个。 三、电池技术特点与适用场景 铅酸电池:价格低廉、技术成熟、安全易回收且低温性能稳定,但重量大、续航短、寿命相对较短且需定期维护,适合价格敏感、短途骑行且充电便利的用户。 锂电池:具备高容量密度、长续航(寿命约5-8年)、强放电性能和起步快的优势,缺点是成本高、低温性能较差(不适用高寒地区)且需保护电路,适合预算充足、追求性能的用户。 钠电池:性能介于铅酸与锂电之间,其充放电倍率和寿命优于铅酸电池,但在容量密度等方面弱于锂电池。随着供应链成本下降,钠电池有望逐步取代铅酸电池,发展前景广阔。 四、地域分布与产业聚集 从通过认证的产品地域分布来看,台州和南京数量最多,分别为44款和41款;其次为无锡(16款)、深圳(14款)、天津(13款)和重庆(10款)。总体来看,江浙地区在电动自行车充电器认证数量上处于领先地位,这与当地电动自行车产业高度聚集密切相关。 五、输出电压与功率分布分析 在通过新国标3C认证的电动自行车用充电器中,其输出电压大致可分为53V、48V、36V、24V四种,所占比例分别为12%、82%、5%和1%。 在输出功率方面,144W功率产品占比最高,达44%,共计71款;其次是96W功率,占比15%,共24款;86.4W产品占比11%,共18款。可见低功率段充电器占据市场主流。 目前通过认证的充电器输出功率普遍在300W以下,用户完成0-100%充电通常需4小时以上,等待时间较长。而500W以上的高功率充电器多为旗舰锂电车型配置,面向极客用户,价格较高。从中低功率产品占主导的市场结构来看,中低端电动自行车仍是消费基本盘。 六、关键元器件技术参数 在电动自行车充电器设计中,高性能分立器件对提升充电效率与安全性至关重要。MDD系列MOSFET具备以下核心优势: 1、高耐压与可靠性:Bvdss达650V,耐压值高,能有效应对充电过程中的电压波动,提升系统稳定性与安全性,符合新国标对充电器安全性的严格要求。 2、低导通电阻:RDS(ON)值低至0.42Ω(如MDD20N65F),导通损耗小,充电能效高,有助于减少发热,延长充电器寿命,尤其适合中高功率充电应用。 3、强电流处理能力:支持10A-20持续电流,抗冲击性好,满足频繁充放电场景下的高可靠性需求,适配锂电、铅酸等多种电池类型充电器。 4、封装与散热优化:采用TO-220F等封装,散热性能良好,便于设计紧凑型高功率密度充电器,契合二轮车充电器小型化、轻量化趋势。 MDD分立器件以其高性能和高可靠性,可为新国标二轮车充电器提供核心元器件支持,助力产品通过认证并提升市场竞争力。 七、选型推荐 MDD分立器件以其高性能和高可靠性,可为新国标二轮车充电器提供核心元器件支持,助力产品通过认证并提升市场竞争力。

MDD辰达半导体 . 2025-09-24 670

艾迈斯欧司朗展示OLED屏下光谱颜色传感技术

艾迈斯欧司朗(SIX:AMS)今日在深圳举办了“真彩视界:舒适亮度 智显本色”圆桌论坛,聚焦高精度环境光传感的新机遇。本次论坛汇聚了产、学、研各界专家及专业摄影师,共同探讨智能手机显示屏色彩与亮度管理的未来发展趋势。 随着OLED屏幕在智能手机市场的普及率持续攀升,消费者对显示质量的关注已不再局限于分辨率、对比度等基础参数,而是逐步扩展至屏幕对环境光的智能响应能力以及自适应护眼视觉体验。专业图像质量测评机构DXOMARK指出,显示屏不应仅作为被动组件存在——它们正日益成为用户体验的主动塑造者。与此同时,TÜV莱茵(TÜV Rheinland)也升级了其认证标准,将护眼性能、动态显示特性及环境光适应性纳入显示屏的综合评价体系之中。 艾迈斯欧司朗举办圆桌论坛活动,探讨智能手机显示屏色彩与亮度管理的未来发展趋势 差异化体验:通过色彩调节,打造最佳用户体验与舒适用眼感受 香港理工大学魏敏晨教授表示:“优秀的显示技术,应做到‘视觉无形,体验有感’。色彩还原绝非单纯的技术参数比拼,它对实现健康、自然的视觉体验至关重要。影响屏幕色彩真实性与一致性的关键在于硬件品质、出厂校准、环境光自适应、内容映射以及长期使用的稳定性等多重因素的协同配合。只有经过仔细优化,才能为用户带来最舒适、最自然的视觉感受。” TÜV莱茵大中华区电子电气产品服务区域总经理刘喜强则表示:“面对消费者对用眼健康的需求,TÜV从护眼技术、动态显示特性和环境光管理三个维度构建了显示屏护眼能力的评估体系。艾迈斯欧司朗的屏下光谱技术通过精准的环境光管理,确保了用户在不同场景下都能获得始终如一的舒适体验,为终端设备的健康显示树立了新的技术标杆。” DXOMARK产品市场总监Fabien Montagne认为:“屏幕显示至关重要。我们的研究结果表明,具备先进色彩自适应功能的智能手机对提升用户体验起着关键作用。艾迈斯欧司朗的创新技术能精准捕捉环境光特性,助力设备动态适配环境光、视觉环境等外部因素。目前,我们仍高度关注‘拍照的差异化特色’,该差异化特色可体现不同厂商在曝光、色彩等方面的差异化战略选择。同样,‘显示的差异化特色’也应该得到多维度的全面发展,以满足不同用户场景下的需求多样性。” 百万粉丝摄影博主@数码王小机团队的石新宇从用户实际使用场景出发,分享了该技术带来的体验升级。他表示:“在摄影创作的过程中,用户既渴望真实的影像还原,也需要恰到好处的视觉冲击力。色彩精准的智能手机不仅能帮助创作者忠实记录光影细节,还能让作品与观众产生情感共鸣。屏下光谱技术让屏幕能够智能适配环境光,既保障了创作端的色彩可靠性,也提升了用户端的观看一致性——这对整个内容生态而言都具有重要意义。” 精准环境光特性分析,引领屏幕视觉体验未来 通过本次圆桌论坛,艾迈斯欧司朗展示了其新一代OLED屏下光谱显示技术,进一步巩固了在高精度环境光传感领域的领导地位。依托尖端光感创新技术与深厚的用户洞察,艾迈斯欧司朗将与学术界、DXOMARK、德国莱茵TÜV等合作伙伴携手,助力显示行业与智能手机行业摆脱单纯的“参数竞争”,迈入以“用户体验为核心”的显示技术新时代。 艾迈斯欧司朗ALS & Prox产品线负责人Marcel Knecht发表主题演讲 艾迈斯欧司朗ALS & Prox产品线负责人Marcel Knecht表示:“显示质量已成为高端智能手机实现差异化的核心要素。我们的环境光传感解决方案显著提升了OLED显示屏的精准适配能力,助力手机制造商更好地满足消费者期待,赢得市场竞争优势。” 艾迈斯欧司朗新一代OLED屏下光谱传感技术亮点 采用专有滤光技术,可获得高精度色度数据——在LED光源主导的复杂照明环境中至关重要; 在低透光率OLED显示屏(约3%至<1%)及宽视场条件下仍保持卓越性能; 凭借快速数据采样与先进算法,不受高频PWM调光影响,实现稳定的环境光传感。 艾迈斯欧司朗IOS事业部研发负责人Dalibor Stojkovic解析OLED屏下光谱传感技术亮点 艾迈斯欧司朗IOS事业部研发负责人Dalibor Stojkovic认为:“我们开发了一系列创新技术,涵盖滤光片、光学元件及传感器芯片等多个领域。这些技术突破,大幅提升了环境光传感器的测量精度。未来,艾迈斯欧司朗将持续携手行业领先合作伙伴,依托这些尖端解决方案,共同推动实现‘色彩还原总能精准呈现预期显示效果’与‘舒适护眼’的双重愿景。”

艾迈斯欧司朗 . 2025-09-24 555

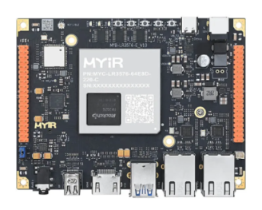

360环视硬件平台为什么推荐使用米尔RK3576开发板?

在汽车智能化和智慧安防快速发展的今天,360环视系统 已成为保障行车与场景安全、提升体验的重要技术。无论是自动泊车、驾驶辅助,还是智慧社区监控,核心诉求都是能够接入 多路摄像头,并通过高效的 推流 实现低延迟显示与存储。然而,传统硬件平台在接入路数、实时性与稳定性方面常有瓶颈,难以支撑更大规模、更高质量的视频处理场景。 为此,越来越多的企业在构建360环视硬件平台时选择 米尔RK3576开发板。凭借先进的 SoC 架构与完善的多媒体引擎,它不仅具备 12路摄像头 的高清视频接入能力,还能将编码与 RTSP 低延迟推流 组合成体系化方案,为360环视提供稳定可靠的底座。 米尔RK3576开发板 一、360环视的核心技术需求 · 多路摄像头实时接入:360环视通常涉及前、后、左右及顶置等多角度画面,实际工程中对路数的要求常常在 8~12 路甚至更多。 · 高效推流与低延迟:泊车与行驶场景对实时性敏感,端到端延迟需要尽量压低,一般建议控制在 200ms 以内。 · 高清视频与高效编码:在保证 1080P 画质的同时,需要尽可能提升编码效率以节省带宽与存储成本。 二、米尔RK3576开发板的关键优势 强大性能架构:RK3576 采用先进 8nm 工艺,集成 四核 Cortex-A72(2.2GHz)+ 四核 Cortex-A53(2.0GHz) 的大小核架构,配合 Mali-G52 MC3 GPU 与 6TOPS NPU,可兼顾高清视频处理与 AI 识别/融合计算。 12路摄像头接入:通过 3 路 4-lane MIPI-CSI 与配套转换模块,可并行接入 12 路 1080P@30fps 摄像头画面,天然契合 360 环视的多视角覆盖诉求。 低延迟 RTSP 推流:在米尔优化方案中,RK3576 将多路视频进行 RGA 图像预处理与 VPU 硬件编码(H.264),经网络 RTSP 推流 到接收端解码显示,端到端延迟约 120~150ms(编码侧 80~100ms + 传输/解码 40~50ms),满足车载与安防对实时性的要求。 资源均衡与稳定可靠:RGA、VPU、CPU、GPU 等模块各司其职,负载均衡、长时运行稳定,有利于工程化落地与规模部署。 三、360环视典型应用场景 · 车载环视与自动泊车:融合 12 路多视角画面,提供车辆周边全景视野,显著提升泊车安全与驾驶体验;NPU 可同时用于目标检测与轨迹辅助。 · 智能安防监控:多路摄像头同时接入,支持高清实时推流与录像回放,实现园区/工地/商用场所的无死角覆盖。 · 工业视觉处理网关:在产线侧对缺陷、动作与工序进行识别与统计,多路同步更利于跨工位协同与对比分析。 · 智慧社区 AI 防控:基于 6TOPS NPU 可扩展高空抛物、陌生人闯入、电动车进电梯等识别场景,实现前端边缘智能与快速响应。 RK3576获取12路 摄像头数据编码传输数据到板子显示过程 四、总结与获取更多信息 综上,米尔RK3576开发板以 多路摄像头 并发接入、12路摄像头 高清处理与 低延迟推流 的方案能力,构建起 360 环视的坚实硬件底座;在车载、安防、工业与社区等多元场景中,兼具高效、稳定与可扩展性。 想了解更多关于米尔RK3576核心板/开发板的详细信息? 欢迎访问我们产品页面:https://www.myir.cn/shows/151/81.html

原创 . 2025-09-24 635

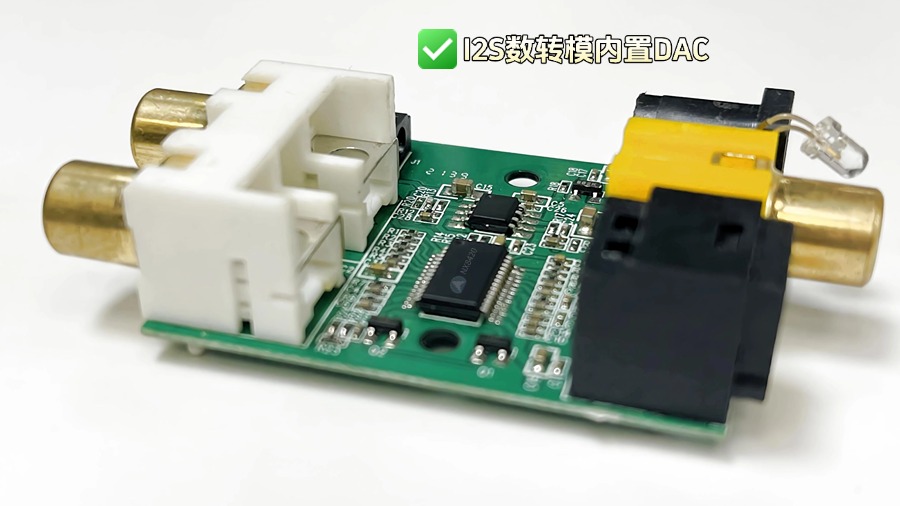

纳祥科技NX8420,一款抖动性能低至 200ps的192KHZ数字音频接收器

NX8420 是纳祥科技推出的一款 192kHz 数字音频接收器,专为高保真音频传输设计,支持 S/PDIF 和 AES/EBU 等主流数字音频接口标准。 其核心功能包括:多通道音频处理;内置多路复用器,可同时接收最多 5 通道数字音频输入数据,并支持 S/PDIF 直通功能,提升系统灵活性;通过极低抖动时钟恢复机制(抖动性能低至 200ps),确保从输入音频流中生成高精度时钟信号。 NX8420 兼容IEC-60958、EIAJ CP1201、AES3等标准,性能远超其他产品,适用于消费级和专业音频设备。 ▲NX8420芯片主图 (一)NX8420主要特性 作为一款I2S数字转模拟内置DAC,NX8420具有以下特性—— ①支持EIAJ CP1201,IEC-60958, S/PDIF和AES3接口标准 ②3.3V-5V供电 ③4:1 S/PDIF多路输入 ④AES/PDIF硬件输入选择 ⑤S/PDIF至TX输入 ⑥32-192KHz采样率 ⑦Muti-bit Δ∑调制器 ⑧100dB 动态范围 ⑨-75dB 总谐波失真+信噪比 ⑩低时钟抖动敏感度 ⑪线性滤波输出 ▲NX8420框架主图 (二)NX8420芯片优势 NX8420 是一种单片 CMOS 器件,I2S数转模内置DAC,其具有以下产品优势—— ①低功耗、低失真 NX8420 采用3.3V-5V 供电设计,确保低电压下稳定运行,提升能效;具有100dB 动态范围、-75dB 总谐波失真+信噪比,展现极低失真性能,提供纯净音频信号。 ②散热小封装 NX8420采用TSSOP28封装,具有较小的尺寸和较好的散热性能,有利于提高电路板的集成度和降低产品成本。 ③灵活适配各种数字音频设备 作为一款音频收发器,NX8420支持多种数字音频接口标准,可以输入/输出24、20或16位的数字音频。输入数据可以完全与输出数据异步,同时输出数据可与以外部系统时钟同步。可实现AES3信号与I2S信号的相互转换。 ▲NX8420管脚排列图 (三)NX8420应用领域 NX8420是一款高性能的I2S数字转模拟内置DAC,因其具有广泛的市场前景和发展潜力,被应用于音频处理、专业音频设备等领域,包括 A/V 接收器、CD-R、DVD 接收器、多媒体扬声器、数字混音控制台、特效处理器、机顶盒、计算机和汽车音响系统等。

数字音频接收器

深圳市纳祥科技有限公司微信公众号 . 2025-09-24 545

瑞萨电子超低功耗RA0系列新增电容式触控功能MCU

低成本RA0L1系列产品面向消费电子、小型家电及工业系统控制领域 瑞萨电子今日宣布推出基于Arm® Cortex®-M23处理器的RA0L1微控制器(MCU)产品群。该系列具备超低功耗特性,为电池供电设备及其他消费电子、家电、白色家电,及工业系统控制领域提供业界卓越的电容式触控解决方案,助力客户实现快速且经济的部署。 瑞萨于2024年推出的RA0 MCU系列凭借其经济性与低功耗优势,赢得众多客户的青睐。RA0L1系列在延续这些优势的基础上新增电容式触控功能,使设计人员能够以极低成本打造响应灵敏、外观精美且低功耗的用户界面。 RA0L1系列MCU拥有业界优异的功耗表现:工作模式下电流低至2.9mA,睡眠模式下仅0.92mA。此外,该系列还集成高速片上振荡器(HOCO),具备同类产品最快的唤醒速度。快速唤醒功能使RA0L1 MCU能更长时间保持待机模式,且功耗降至微不足道的0.25μA,较其它解决方案电流消耗降低达90%。 针对低成本优化的功能集 RA0L1系列的功能集专为成本敏感型应用优化。其工作电压范围宽达1.6V至5.5V,客户在5V系统中无需额外配置电平转换器/稳压器。该系列MCU还集成多种通信接口、模拟功能、安全功能及安全机制,有助于降低客户BOM成本。产品提供包括4mm×4mm 24引脚QFN微型封装在内的多种封装选项。 此外,新型MCU搭载的高精度(±1.0%)HOCO可提升波特率精度,使设计人员无需使用独立振荡器。与业界其它HOCO不同,该振荡器在-40°C至125°C环境下均能保持这一精度。宽温特性让客户无需在回流焊后进行耗时且成本高昂的“微调”,即可简化热设计。 瑞萨在电容式触控技术领域的卓越优势 瑞萨提供业界优异的电容式触控技术,助力客户在各类系统中快速、经济地实现高品质触控界面。其自电容法可简化防水设计,相比互电容方案可降低设计复杂度。瑞萨的多频测量技术符合IEC61000-4-3的第4级标准,适用于需要较强效抗电磁干扰防护的医疗应用。此外,瑞萨还提供专用的电容式触控开发资源,包括QE for Capacitive Touch工具,可简化电容式按键的灵敏度调节,加速开发进程。 Daryl Khoo, Vice President of the Embedded Processing Marketing Division at Renesas表示:“RA0L1融合了RA0系列MCU在功耗和成本效益方面的优势,以及我们卓越的电容式触控技术与工具。我们期待客户运用这些器件,创造出更多创新的触控界面解决方案。” RA0L1产品群MCU的关键特性 内核:32MHz Arm® Cortex®-M23 存储:最高64KB,集成代码闪存及16KB SRAM 扩展温度范围:环境温度-40°C至125°C 定时器:定时器阵列单元(16位×8通道)、32位间隔定时器(8位×4通道)、RTC 通信外设:3个UART、2个异步UART、6个简化SPI、2个I2C、6个简化I2C 模拟外设:12位ADC、温度传感器、内部基准电压 HMI:电容式触控(最多24通道)、受控电流驱动端口(最多8个) 安全特性:SRAM奇偶校验、无效内存访问检测、频率检测、A/D测试、输出电平检测、CRC计算器、寄存器写保护 安全机制:唯一ID、TRNG、闪存访问窗口、闪存读保护 封装:24/32/48引脚QFN、32/48引脚LQFP、20引脚LSSOP 全新RA0L1产品群MCU由瑞萨灵活配置软件包(FSP)提供支持。FSP提供所需的所有基础架构软件,包括多个RTOS、BSP、外设驱动程序、中间件、连接、网络和安全堆栈,以及用于构建复杂AI、电机控制和云解决方案的参考软件,从而加快应用开发速度。它允许客户将自己的既有代码和所选的RTOS与FSP集成,为应用开发带来充分的灵活性。借助FSP,客户可简化与其它RA系列产品之间相互迁移的过程。 成功产品组合 瑞萨将全新RA0L1 MCU产品群与其产品组合中的众多可兼容器件相结合,创建广泛的“成功产品组合”,包括电容式触摸遥控器。“成功产品组合”基于相互兼容且无缝协作的产品,具备经技术验证的系统架构,带来优化的低风险设计,以加快产品上市。瑞萨现已基于其产品阵容中的各类产品,推出超过400款“成功产品组合”,使客户能够加速设计过程,更快地将产品推向市场。 供货信息 RA0L1产品群MCU以及FSP软件现已上市,同步推出RA0L1快速原型开发板和RA0L1电容式触摸评估系统。客户可以在瑞萨网站或通过分销商订购样品及套件。 瑞萨MCU优势 作为全球卓越的MCU产品供应商,瑞萨电子MCU近年来的平均年出货量超35亿颗,其中约50%用于汽车领域,其余则用于工业、物联网以及数据中心和通信基础设施等领域。瑞萨电子拥有广泛的8位、16位和32位产品组合,所提供的产品具有出色的质量和效率,且性能卓越。同时,作为一家值得信赖的供应商,瑞萨电子拥有数十年的MCU设计经验,并以双源生产模式、业界先进的MCU工艺技术,以及由250多家生态系统合作伙伴组成的庞大体系为后盾。

瑞萨电子 . 2025-09-24 435

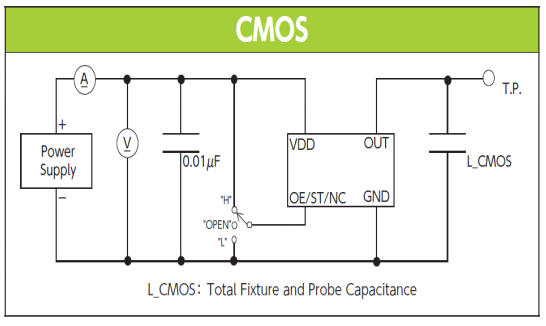

有源晶振的线路图引脚图

普通有源晶振有4个脚,有个缺角位的我们称之为1号脚(PIN1)或脚#1,按逆时针(管脚向下)分别为2、3、4。 Pin#1三态/悬空(TRI-STATE/NO CONNECTION) Pin#2接地(Ground) Pin#3接信号输出(Output) Pin#4接电源电压(VDD) 但需要指出的是,针对不同有源晶振型号,在接法上也存在一定差异。如果晶振Pin#1具备E/D使能功能或Stand-by待机功能,接地(Ground)就会导致晶振无法输出频率信号。因此,接线前请务必仔细阅读规格书中相关说明,以免发生错误接线后引发有源晶振工作不良。 如下图所示: 有源晶振内部含有石英晶体、振荡IC和匹配电容等外围电路,精度高、输出信号稳定,不需要设计外围电路、使用方便,但需要电源供电。使用有源晶振时要特别注意,电源必须是稳压的且电源引线尽量短,并尽量与系统中使用晶振信号的芯片共用一个GND。

有源晶振

扬兴科技 . 2025-09-24 1 420

【天源中芯TP4337】你的充电宝还好吗?国产芯片安全范本来了!

2025 年夏季,消费电子行业因电芯材料违规替换引发的系统性危机,暴露出供应链透明度不足、检测能力滞后等深层问题。在这场行业地震中,移动电源核心芯片的安全防护能力成为破局关键。天源中芯半导体推出的TP4337 1A同步移动电源解决方案,以单芯片集成化设计与多重智能保护机制,为行业提供从芯片级到系统级的安全升级范本。 一、单芯片集成:安全与效率的双重突破 TP4337作为全集成电源管理SOC,将线性充电管理、同步升压转换、电量指示与六大安全保护功能集成于ESOP-10L封装中,较传统方案,外围元件减少约30%,直接降低BOM成本。其核心技术亮点直击行业痛点: 1. 智能温控三重防护网 • 梯度降流机制 当芯片温度升至 115℃时,自动线性降低充电电流,避免传统方案骤停导致的充电中断,可延长有效充电时间; • 硬件级关断保护 温度触及150℃时瞬间切断电路,降温至 130℃后自动恢复,响应时间<10ms(根据短路保护延时 TSHORT=500μs计算),优于行业平均20ms的保护速度; • NTC 电池温度闭环 外接100kΩ/B3950K热敏电阻构建温度反馈网络, 充电时0-45℃全速充、>45℃或< 0℃停充;放电时-10-60℃正常工作,超出范围立即停机,精准匹配锂电池安全工作区间。 2. 六重安全防护联动 芯片内置过充/过放保护、输出过压/过流/短路保护,以及芯片温控与NTC双回路温度保护。其中短路保护具备自动复位特性,移除负载后即可重新启动,避免因偶发故障导致的整机报废。 二、从参数到场景:安全能力的全维度落地 在实际应用中,TP4337通过细节设计将安全指标转化为用户可感知的体验升级: 1. 边充边放与低功耗管理 集成电源路径管理,支持充电时同步升压放电,当电池电压> 3.1V 时自动启动输出。待机状态下电流低至10μA,轻载关机电流50mA,配合负载自动检测功能,可避免传统方案因待机功耗高导致的电池亏电问题。 2. 电量指示与应急功能 支持4灯/2灯两种电量指示模式:充电时按电量梯度点亮LED并闪烁提示,充满后全亮;放电时低于3.05V触发LED快闪报警,低于2.8V自动停机。此外,长按按键2秒可开启60mA手电筒功能,在低电量时自动屏蔽以保护电芯。 三、产业启示:芯片定义安全的新范式 此次充电宝危机本质是 “成本优先” 逻辑的反噬,而TP4337的实践证明:通过芯片集成化可释放约20%的BOM成本空间,其中8%可用于陶瓷涂层隔膜等安全材料升级,5%用于双泄压阀结构,7%构建全链路追溯系统,形成 “安全-成本-体验” 的正向循环。 目前TP4337已落地移动电源(电池容量≤5000mAh)、应急电源等场景,工程师可申请样品,最快1周内即可完成方案验证。 TP4337典型应用电路图(2灯模式)▲ TP4337典型应用电路图(4灯模式)▲ 当供应链风险倒逼产业升级,芯片从 “功能提供者” 转变为 “安全定义者”。TP4337 以单芯片方案重构移动电源安全基线,不仅为品牌商提供规避召回风险的技术工具,更推动行业从 “事后补救” 转向 “事前预防” 的发展范式。 本文转自芯片原厂【深圳天源中芯半导体有限公司】官方账号,如有任何疑问,可访问天源中芯官网咨询。欢迎关注天源中芯公众号随时了解更多优质国产芯片(公众账号中搜索“天源中芯”加关注)。

国产芯片

天源中芯公众号 . 2025-09-24 1155

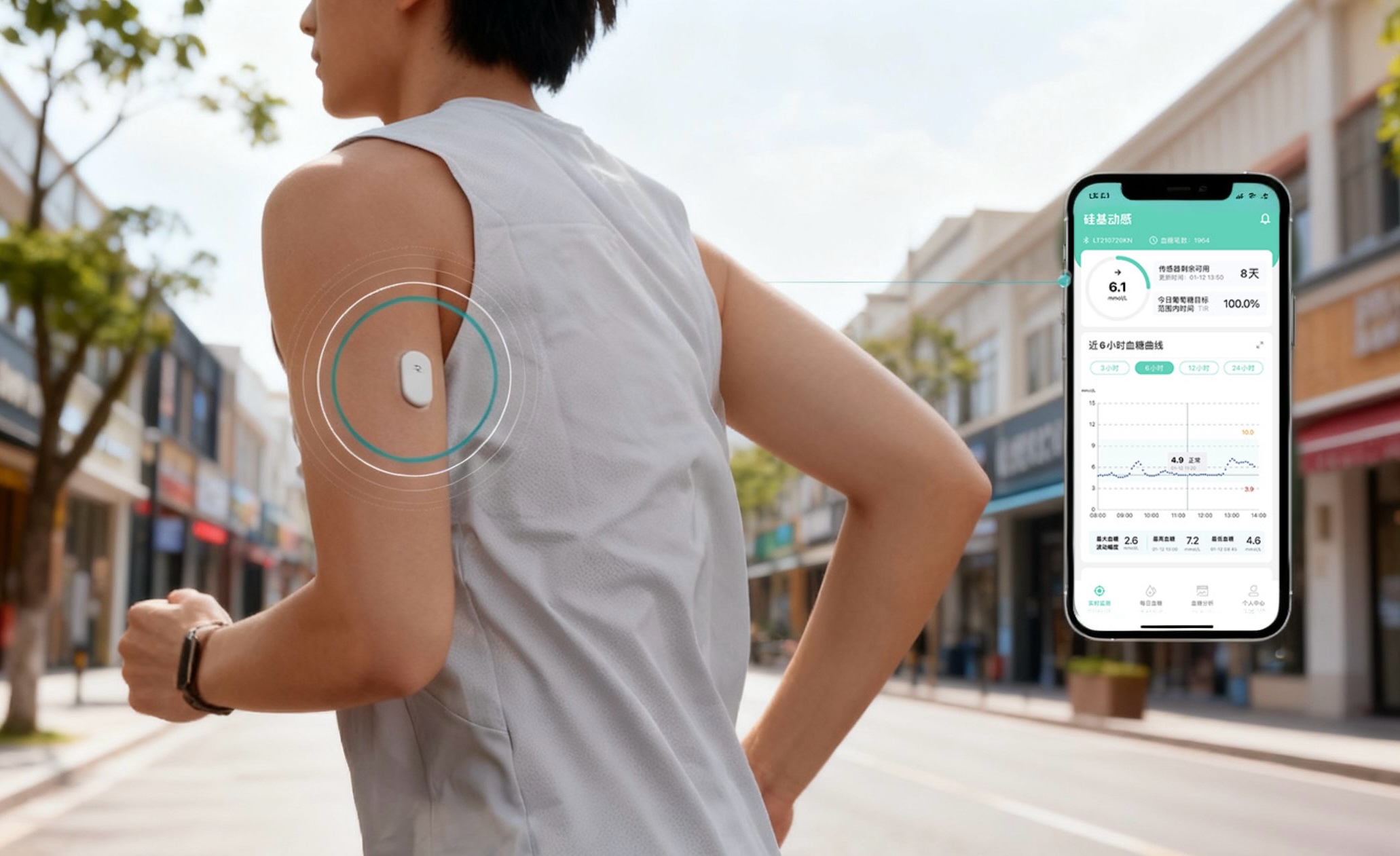

产品 | 微创血糖监测:艾为Hyper-Hall™突破体积、续航、性能,助力CGM新未来

据权威数据统计,2024年全球成人糖尿病患者为5.89亿,预计2050年将突破13.1亿,如何实现更精准、更便捷的血糖管理,成为医疗行业的焦点。在此背景下,作为糖尿病管理领域的新兴技术,连续血糖监测仪(CGM)正以实时、精准的监测优势重塑患者照护模式,为临床诊疗与日常健康管理提供全新解决方案。 图1 连续血糖监测仪(CGM)使用场景 进一步聚焦技术核心痛点,怎样在设备微型化设计的基础上,兼顾持久待机需求与实时数据传输的可靠性,确保监测数据准确、及时反馈。这三大问题已成为CGM 行业发展的核心瓶颈,也是技术研发与产品创新的重要方向。 中国数模龙头艾为电子以核心产品Hyper-Hall™ 构建磁传感器产品全品类布局,为进一步明晰技术路线、精准覆盖不同市场领域,同时帮助消费者快速辨识产品特性、感知核心技术价值,艾为电子将Hyper-Hall™细分为三大产品系列: S 系列(Steady,聚焦稳定可靠,满足基础需求的场景) R 系列(Rugged ,主打坚固耐用,适配复杂工况高可靠性场景) X 系列(X-accelerate,追求极致超越,以突破性技术性能赋能高端场景,实现产品体验和技术指标的双重领先) AW86501BDC核心优势 AW86501BDC作为 Hyper-Hall™ X 系列霍尔传感器的家族成员,凭借多项核心技术优势树立行业标杆: 其一,实现业内领先的超低功耗,仅 50nA的工作电流可直接对标TMR级产品,为设备续航能力提升奠定关键基础; 其二,采用 1×1mm 超小尺寸封装,极大节省 PCB 板空间,适配CGM微型化产品设计需求; 其三,内置外部杂散磁场抑制功能,有效抵御环境干扰,保障数据传输的高可靠性。 AW86501BDC Hall 传感器攻克“空间受限、续航焦虑、环境干扰”三大核心痛点,从底层为产品提供“微型化空间适配、长周期货架期保障、高稳定性能支撑”的三重关键赋能。 AW86501BDC产品特性 超低工作电压,超低功耗 宽电压输入:1.2V-3.6V(支持1.5V SR系列&3V CR 系列纽扣电池供电) 采用NPC 技术实现50nA超低工作电流,提升 CGM 货架期续航至2年 突破功耗极限,宽电压输入,续航能力行业领先 图2 功耗对比 超小型封装提升设备小型化 外形尺寸1*1*0.4(max)mm,可最大程度降低安装空间,提升CGM无感佩戴体验 Hyper-Hall™ 系列封装面积相比传统系列封装面积降低约90% 图3 封装面积比较 强抗干扰,可靠性更胜一筹 支持Latch锁存功能,驱动能力高达20mA 抵御外部杂散磁场干扰,保证血糖数据实时传输更可靠 图4 强抗干扰输出对比图 中国数模龙头艾为电子始终以技术创新为驱动,通过此类高价值传感器产品,持续为提升医疗健康管理的便捷性、推动健康监护设备的性能升级贡献力量。

传感器

艾为官网 . 2025-09-24 25

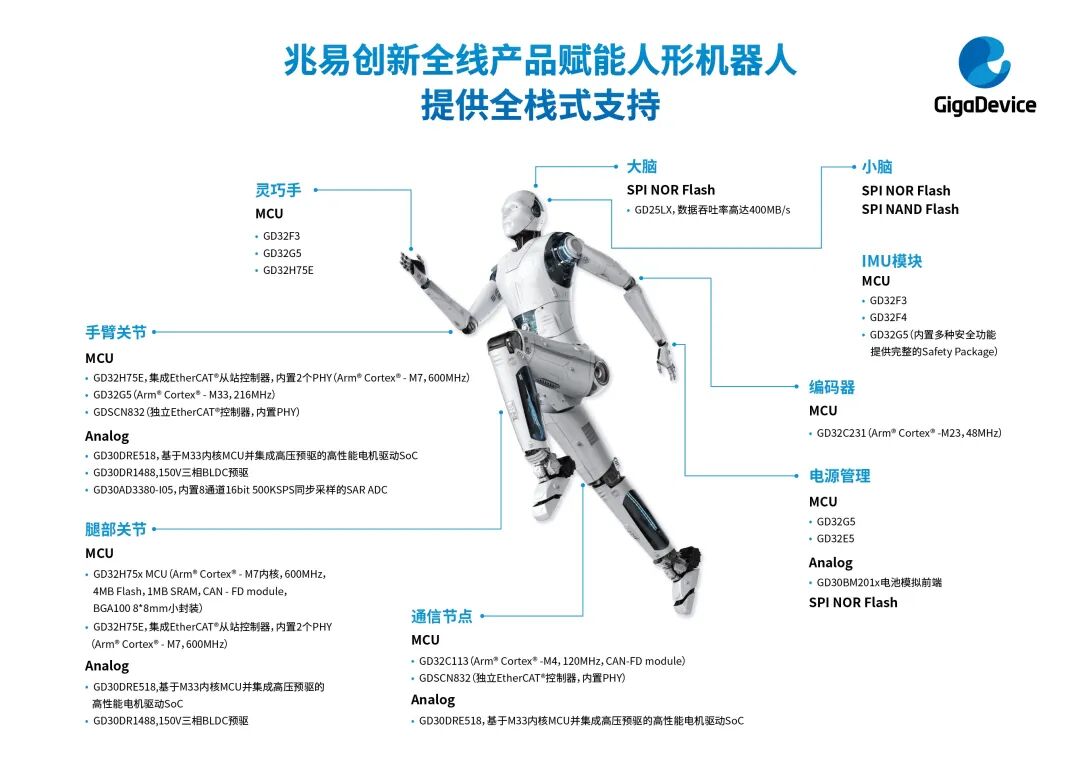

应用 | 2025迎人形机器人量产拐点,兆易创新全栈芯片已就位

从春晚舞台到世界机器人大会,人形机器人已经不再是舞台上的木偶,开始向真正的生产力工具过渡。2025年是中国人形机器人走向规模化量产和商业落地的关键年份,众多头部企业纷纷宣布重大进展。根据公开数据显示,优必选Walkers系列获车厂超500台订单并拿下2.5亿元大单;智元机器人计划下半年规模出货,预计2026年达数千台产量;宇树科技年量产目标超5000台,推出仅 3.99万元的轻量版产品。 而硬件系统的成熟,正是人形机器人实现规模化量产与商业落地的重要基础。其环境感知、运动控制与任务执行能力,依赖于感知层、旋转关节、直线关节、整体躯干、灵巧手、机器脚六大核心单元的高效协同;在这一架构中,芯片的性能与高效的通信更是直接决定机器人的实时响应速度与智能水平。 在芯片赋能机器人硬件的赛道上,兆易创新凭借多年技术积累,构建覆盖控制、存储及模拟的完整产品矩阵,为人形机器人提供全栈式芯片支持。其中,GD32高性能MCU可用于多关节实时运动控制与系统调度;旗下Flash为决策计算提供高速高可靠的数据存储保障;模拟芯片更覆盖传感器信号调理、电机驱动、电源管理等关键环节,从感知、决策到执行全链路赋能机器人系统。 完善矩阵赋能精准控制 运动控制系统如同人形机器人的小脑,负责根据目标轨迹和负载状态,协调驱动器控制执行电机完成精确动作。在这一系统中,MCU作为主处理器的神经末梢,分布于各关节,承担指令接收、电机驱动、编码器/IMU数据处理及力矩、位置、速度的闭环控制。这种分布式架构有效降低主控负载,保障动作的低延迟、高精度与多关节协同,是实现灵活稳定运动的核心基础。 灵巧手空间受限且电机密集,对高集成度MCU需求迫切。GD32G5系列凭借单芯片驱动多电机的能力脱颖而出。以GD32G553为例,其采用Arm® Cortex®-M33内核,主频高达216MHz,集成DSP指令集、单精度FPU及硬件三角函数加速器(TMU),算力强劲,可轻松实现单电机精密控制或同时驱动3至4个电机。同时,其WLCSP81封装尺寸仅4×4mm,极大节省空间,三颗芯片即可覆盖灵巧手全部关节,显著优化布局与成本。 人形机器人中的关节众多,对驱动的要求各不相同,如腿部负责支撑与动态平衡,需实时计算步态并调整姿态,对算力要求更高,GD32H7系列就非常适用。其搭载600MHz Cortex®-M7内核,配备双精度FPU、TMU及滤波算法加速器(FAC),集成CAN-FD、以太网等工业接口,能够在单芯片上完成多传感器数据融合,广泛用于人形机器人腿部关节及机器狗中。 EtherCAT®总线在人形机器人中广泛用于整合关节、传感器与控制器通信,若采用该协议,GD32H75E是理想之选。该芯片在GD32H7基础上集成正版授权的EtherCAT® IP,内置2颗百兆以太网PHY,支持μs级多轴同步,满足复杂运动场景下高速、低延迟通信需求,可用在需执行精细抓取等任务、控制精度要求高的手臂关节中。除了超高的集成度外,GD32H75E还支持105℃环温运行,具备BGA144(8×8mm)小封装,解决了机器人关节空间狭小、运行温度较高的痛点。 通信节点负责机器人部件间协议解析与指令转发,GD32C113系列可满足需求。采用Cortex®-M4内核(最高120MHz),该系列还支持2路高速CAN- FD。若用EtherCAT®协议,可选2/3端口的GDSCN832从站控制器,其集成2个内部PHY、1个MII扩展接口,配备8KB双端口内存,为复杂控制提供大数据处理能力。 整体而言,兆易创新GD32 MCU可与GD30DR系列驱动芯片协同,配合LDO、DC-DC、PWM及保护电路,构建完整、可靠的机器人电机控制解决方案,全面服务于关节驱动与伺服系统。 与GD32 MCU相配合,兆易创新的存储产品也在人形机器人中发挥关键作用。其中,GD25/55 X/LX系列SPI NOR Flash拥有400MB/s的数据吞吐量,可满足即时启动及实时响应需求,为执行AI决策的机器人大脑提供高速存储支持。 高性能、高集成度,打破传统瓶颈 在人形机器人系统中,模拟产品的作用同样关键,兆易创新亦构建了覆盖核心需求的完善模拟产品矩阵,多款重磅产品为机器人精准控制与稳定运行提供支撑。 GD30AD3380 GD30AD3380是一款8通道16bit同步采样的高性能ADC,采样速率最高可以到1MSPS,支持真双极性硬件与软件模式,可实现每通道独立输入范围配置,并通过SPI、并行总线等灵活接口传输数据。其同步采样特性适配高精度感知需求,可广泛应用于机器人外骨骼、灵巧手的六维力矩传感器的数据转换,实现运动系统对关节及承重结构的力与力矩信息的精准捕捉,配合相关算法实现细腻流畅的运动控制。 GD30DR1488 GD30DR1488则是专为机器人关节三相无刷直流电机(BLDC)设计的栅极驱动器,具备150V高电压耐受能力,适配电机工作电压范围;提供+1.0/-1.3A拉灌电流与500kHz最高开关频率,确保驱动响应速度。其核心优势在于内置自举二极管,简化外围设计,减少PCB面积。 GD30DRE518 GD30DRE518是更具集成优势的SoC芯片。该SoC采用基于Cortex®-M33内核的MCU并集成最高耐压为150V三相BLDC预驱,其MCU最高主频为180MHz,搭配512KB闪存、128KB SRAM,并提供16个通道12bit ADC,3个通道12bit DAC,同时提供多通道的高级、常规通用定时器,以及丰富的接口资源,包括3通道CAN-FD、SPI/I2C/USART/GPIO等。它可同时承担节点通信、电机驱动与传感器数据运算任务,打破传统电机驱动SoC芯片仅能驱动电机、无法处理其他复杂任务的局限。 相较于传统模拟方案,兆易创新模拟产品优势显著:不仅突破功能单一性,凭高集成度实现小型化,更能应对各类严苛需求。深究其模拟产品线的竞争力,源于三大核心支撑:一是依托MCU等产品线、技术沉淀与人才团队,实现技术协同复用;二是凭借多年积累的客户生态,聚焦机器人等优势行业,打造多产品线协同方案,精准匹配场景需求;三是依靠战略持续投入,结合优质供应链与一流质量体系,为客户提供可靠且具性价比的产品。 结语 2025年被视为人形机器人迈向规模化量产的关键拐点,预计将带动高精度电机控制、多模态传感与边缘计算芯片需求的显著增长。为应对这一趋势,兆易创新将重点布局伺服驱动实时控制、完善的模拟产品组合、高性能存储产品等方向,为客户提供高性价比的一站式解决方案,助力人形机器人实现核心技术突破与规模化应用。

GD

兆易创新GigaDevice . 2025-09-23 1 2 2125

企业 | 共绘具身未来,ADI携手产业伙伴举行人形机器人媒体分享会

随着人工智能技术的飞速发展,全球机器人产业正迎来前所未有的变革与机遇。日前,全球领先的半导体公司Analog Devices(下文简称:ADI)举行“激活边缘智能,共绘具身未来”人形机器人媒体分享会。作为中国创新生态的一员,ADI与来自北京人形机器人创新中心(国家地方共建具身智能机器人创新中心)、因时机器人与松延动力的产业伙伴代表围绕人形机器人最新成果、未来规划与应用前瞻等内容进行了精彩分享,共同探讨具身智能产业的广阔未来。 ADI助力人形机器人“物理智能”进化 作为自动化领域的先锋,ADI凭借其卓越的感知、连接、控制与解译能力,赢得了业界的广泛赞誉。而人形机器人,正是要将这些能力“浓缩”到一个灵巧的身体里。ADI公司院士兼技术副总裁陈宝兴博士在题为《从数字工厂到人形机器人,全方位构建工业智能未来》的主题演讲中表示,从用于景深测量的 ToF 摄像头模组,到用于实现类人灵巧性的 IMU与触觉传感器,ADI能够提供从核心技术到系统性解决方案的全套产品,进而推动人形机器人加速落地。 ADI公司院士兼技术副总裁陈宝兴博士发表《从数字工厂到人形机器人,全方位构建工业智能未来》主题演讲 谈及人工智能技术对全球机器人产业带来的变革与机遇,陈宝兴博士强调,AI是机器人的“大脑”,负责学习、推理、决策;物理智能是“身体”,负责感知、运动、与环境互动,唯有两者深度融合,机器人才能像人一样灵活、聪明、可靠。当前,ADI的机器人团队正致力于将传感器和执行器模型集成到英伟达的 Isaac Sim 平台。这意味着,机器人团队将在高保真度的数字孪生环境中进行传感器融合、路径规划、手指运动控制等复杂任务的训练,这能够优化机器人在复杂环境中的导航与交互能力,进而训练出可直接部署的控制策略。 陈宝兴博士还负责领导ADI的磁性触觉传感器研发工作。他在演讲中分享了ADI磁耦合触觉传感器的独特优势,“ADI正在开发的磁耦合触觉传感器克服了市场上常见触觉传感器(压阻式、电容式和光学检测式)受环境影响可靠性不足的问题,能够有效抵御水分和温度变化的影响,同时具备屏蔽外界磁场干扰的能力,从而确保了其在复杂环境下的稳定性和可靠性。” “具身天工Ultra”迈向跨场景泛化应用征途 今年4月19日,全球首个人形机器人半程马拉松比赛上,“具身天工Ultra”以2小时40分42秒的成绩跑完21.0975公里,成为首个完赛半程马拉松的人形机器人。而这背后,是北京人形团队的不懈努力。据北京人形品牌公关负责人魏嘉星介绍,研发团队针对“具身天工Ultra”的本体和一体化关节的散热性能、运动控制算法的泛化能力进行持续提升,并通过能耗系统的优化和快速换电技术的应用,使其具备了更强的续航能力。人形机器人只有跨越了稳定性、续航、散热等方面的重重考验,才能真正具备走进各类应用场景的潜力。 北京人形机器人创新中心(国家地方共建具身智能机器人创新中心)品牌公关负责人魏嘉星发表《人形机器人创新实践:从技术突破到应用落地》主题演讲 同时,魏嘉星还强调了通用具身智能平台“慧思开物”对人形机器人跨本体、跨场景泛化应用能力的关键意义。“慧思开物”赋予了机器人聪明的具身大脑和灵活的具身小脑,让机器人具备在不同场景下快速解决问题的泛化能力。未来,具身智能机器人无需为单一垂直场景从零开始定向开发,通过“慧思开物”平台赋能即可快速具备在不同场景中灵活完成多样化任务的能力。 因时机器人打造灵巧手极致性价比 灵巧手是衡量机器人成熟度与商业落地价值的核心标尺。作为国内最早实现五指灵巧手商业化的公司,也是国内目前唯一实现大批量交付的厂商,因时机器人CMO房海南在主题演讲中表示,通过迅速提升批量化生产能力,持续推出高性价比产品,公司2025年上半年的灵巧手销量已达到4000台,而这主要得益于公司将产品底层的技术路线全部都打通,研发出灵巧手的核心零部件产品微型伺服电缸,同时公司在微型伺服电缸上的成功能够进一步去均摊灵巧手的BOM成本。 北京因时机器人科技CMO房海南发表《灵巧手—驱动人形机器人未来的关键力量》主题演讲 经过多年的发展,因时机器人已经推出了5个标准系列的灵巧手产品。“其中,RH56DFX系列凭借其速度与力量的完美平衡,成为过去5年中出货量较大的系列产品,也是在科研和抓取场景中应用最广泛的一款产品。今年推出的F1系列在DFX的基础上做了很多的优化升级,不论是硬件还是软件层面,可以说完全为匹配当前人形机器人需求而生。此外,因时机器人还推出了拥14个主动自由度的RH5EG1系列灵巧手产品。实际上,每增加一个自由度就意味着要增加一个微型伺服电缸,而在有限的空间内,如何在机械结构复杂性增加的情况下,确保产品性能的稳定性和可靠性,这是在开发高自由度产品时需要重点考虑的问题。”房海南如是介绍。 探寻人形机器人商业化突破之路 在从“实验室炫技”迈向工业场景与商业化应用的道路上,人形机器人仍面临多方面的挑战,而这也正是整个产业重点发力的方向。在由ADI中国区工业市场总监蔡振宇主持的“从原型到量产—人形机器人商业化突破之路”的圆桌讨论环节中,与会嘉宾围绕人形机器人的技术发展、潜在挑战及产业展望等话题进行了积极而热烈的观点交流与经验分享。 圆桌论坛:从原型到量产—人形机器人商业化突破之路 在探讨人形机器人商业化所面临的挑战时,四位嘉宾指出了当前亟待解决的关键问题。陈宝兴博士认为,人形机器人需具备对物理环境的认知与自适应能力,才能应用于复杂工业场景,而物理智能发展尚不成熟并构成重要瓶颈。北京人形机器人创新中心(国家地方共建具身智能机器人创新中心)具身天工事业部负责人刘益彰强调,目前,仍须全面提升人形机器人的整体可靠性和稳定性。房海南则指出,硬件方面需实现批量生产,软件方面应持续优化算法,并推动软硬件深度融合。松延动力人形机器人电控系统负责人吴雅剑认为,控制系统的核心零部件和动力成本目前仍居高不下,降低成本也是实现商业化的重要方向。 谈及应对之道,四位专家分享了各自企业的策略。刘益彰表示,创新中心正通过持续技术迭代,致力于实现从底层零部件到机器人系统、再到通用具身智能平台的全链路突破。房海南指出,因时聚焦于一体化线性执行器微型伺服电缸的研发与规模化量产,以高一致性产品服务机器人与新能源领域,并持续优化成本、推动技术迭代以保持核心竞争力。吴雅剑谈到,松延动力机器人之所以能完成空翻等高难度动作,主要依靠算法轨迹优化、模仿学习、强化学习训练,而这一切都建立在稳定的硬件结构基础之上。陈宝兴博士表示,ADI致力于推进物理智能,不仅提供从核心技术到系统性解决方案的全套产品,还注重将人工智能与控制系统深度融合并形成闭环控制。同时,ADI还主张通过构建高精度物理模型和数字孪生仿真平台,预先优化机器人的动作与场景,从而增强系统方案的适应性与可靠性。 谈及未来,四位嘉宾不约而同地表示,人形机器人将率先在工业、物流等环境相对简单的场景中迎来应用爆发。而随着时间推移,机器人有望逐步进入家庭和服务领域。陈宝兴博士表示,从长远看,人形机器人发展的终极目标是实现高度自主的人机交互,使机器人能够陪伴人类、独立规划并完成任务,无需人类指导。 在此次媒体分享会的最后,与会嘉宾与参会记者还共同参观了北京人形机器人创新中心(国家地方共建具身智能机器人创新中心),近距离感受具身智能的独特魅力。 与会嘉宾与参会记者共同参观北京人形机器人创新中心(国家地方共建具身智能机器人创新中心)

ADI

亚德诺半导体 . 2025-09-23 1285

企业 | 英伟达将向OpenAI投资1000亿美元共建10GW AI算力中心

2025年9月22日,英伟达(NVIDIA)与OpenAI联合宣布达成战略合作伙伴关系,双方签署意向书(LOI),计划共建至少10吉瓦(GW)算力规模的AI数据中心,英伟达将按每1GW交付进度逐步向OpenAI投资最高1000亿美元,换取非投票股权。这一合作被业内公认为“AI行业史上最大单笔投资”及“全球AI基础设施史上最大规模资本与硬件捆绑交易”,标志着全球AI算力竞争进入新阶段。 核心合作框架与规模 此次合作的核心在于“资金+硬件”的深度绑定:英伟达承诺提供最高1000亿美元投资,同时OpenAI将进行大规模芯片采购,部署基于英伟达Vera Rubin平台的硬件系统。双方计划分阶段推进10GW算力中心建设,首阶段1吉瓦系统目标于2026年下半年上线,2028年前完成全部10GW部署,最终将配备数百万颗英伟达GPU,用于支撑下一代AI模型(包括ChatGPT继任者及通用人工智能(AGI)相关研发)的训练与运行。 投资规模:1000亿美元(AI行业迄今最大单笔投资) 算力目标:10吉瓦(GW),相当于400万至500万颗GPU算力 硬件当量:约等于英伟达2025年全年预计出货总量(是2024年出货量的两倍) 首阶段上线:2026年下半年(基于Vera Rubin平台) 合作核心条款与实施路径 投资与算力绑定机制 英伟达与 OpenAI 的 1000 亿美元合作核心在于构建“投资 - 算力 - 技术”三位一体的深度绑定机制,通过分阶段触发、硬件采购挂钩的模式,实现双方风险与收益的动态平衡。这一机制既不同于传统股权投资,也区别于单纯的硬件采购协议,而是将资本投入与算力落地进度、技术协同深度进行刚性绑定,形成独特的战略联盟架构。 分阶段绑定的核心设计 合作采用“算力里程碑触发投资”的分阶段机制:总投资 1000 亿美元按每 1 吉瓦(GW)算力部署进度分批注入,每落地 1 GW 对应约 100 亿美元投资。首笔 100 亿美元将在首个吉瓦级数据中心建成后支付(以当时估值为准),后续资金随 2027 年累计 5 GW、2028 年 10 GW 等关键节点逐步释放。投资以非控股股权形式进行,英伟达不获得控制权,OpenAI 非营利母公司保留多数治理权,确保技术路线独立性。 从硬件规模看,10 GW 算力对应 400 - 500 万颗 GPU(接近英伟达 2025 年全年出货总量),需部署约 5.3 万个 NVL144 机柜或 2.7 万个 CPX 机柜,全部采用英伟达下一代 Vera Rubin 平台。这一产能规模意味着双方需在 2026 年 H2 首个 1 GW 系统上线后,以平均每季度超 1 GW 的速度推进部署,对供应链协同与工程落地能力构成严峻考验2。 分阶段实施关键节点 2025 年 Q4:完成合作协议最终签署 2026 年 H2:首个 1 GW Vera Rubin 系统上线,触发首笔 100 亿美元投资 2027 年:累计部署 5 GW 算力,对应 500 亿美元总投资 2028 年:完成 10 GW 全量部署,投资总额达 1000 亿美元 争议:“资金闭环”质疑 市场对合作的争议集中于“资金闭环”质疑。有 观点认为,OpenAI 以现金采购英伟达芯片,而英伟达又将资金以投资形式回流 OpenAI,形成“左手倒右手”的循环。但双方强调,合作核心在于“技术共设计”而非单纯资本运作:协议明确要求协同优化 OpenAI 模型及基础设施软件与英伟达硬软路线图,包括定制化芯片开发、算力调度算法优化等深层合作。 这种技术绑定产生的价值远超资金层面。例如,OpenAI 的超大规模模型训练需求将反向驱动英伟达硬件创新,Vera Rubin 平台的高带宽互联、低功耗设计等特性正是双方联合定义的结果;而英伟达通过深度参与 OpenAI 的算力部署,可获取第一手应用场景数据,优化其数据中心解决方案的通用性。此外,合作还将辐射至微软、甲骨文、软银等生态伙伴,推动 AI 基础设施标准的统一。 总体而言,投资与算力绑定机制既是双方应对 AI 基础设施巨额投入风险的务实选择,也是技术协同深化的战略布局。其成功与否不仅取决于 10 GW 算力的如期落地,更在于能否通过这种“资本 + 技术”的双重绑定,定义下一代 AI 算力中心的技术标准与商业模式。 算力绑定驱动市值创新高,竞争格局加速分化 英伟达与 OpenAI 的合作消息引发资本市场强烈反响。2025 年 9 月 22 日,英伟达股价盘中大涨超 4%,触及历史新高,截至收盘涨 3.93%,市值突破 4.46 万亿美元,年内累计涨幅达 37%,稳居全球市值最高公司地位。 合作的溢出效应带动产业链集体上涨:甲骨文(+5%)、微软(+0.7%)等合作方股价同步走高,AI 算力概念股普涨,费城半导体指数收涨近 1.6%,标普 500 指数创今年第 28 次历史新高3536。与之形成对比的是,博通、AMD 等竞争对手风险加剧——此前博通曾获传为 OpenAI 定制芯片订单,而此次合作标志着 OpenAI 在多供应商策略下进一步向英伟达倾斜,行业竞争格局呈现“强者恒强”态势。 公司 定位 竞争优势 潜在挑战 英伟达 GPU与网络设备供应商 AI芯片市场份额超90%,Vera Rubin架构性能领先 反垄断调查,AMD MI450 Helios竞争 甲骨文 云服务与数据中心运营 OCI托管能力支撑Stargate数据中心 微软Azure的市场份额压制 微软 技术合作伙伴 Azure云服务规模优势 失去OpenAI部分工作负载迁移至OCI xAI 竞争对手 Colossus超算支持X数据训练 算力规模仅为Stargate的1/10至1/20 战略意义里程碑:此次合作标志AI产业从“模型竞争”进入“算力基建竞争”新阶段,10吉瓦算力不仅支撑OpenAI加速AGI研发,更定义了“超大规模AI基础设施”的行业标准,其技术协同与资源整合模式可能成为未来全球科技竞争的模板。 从长期看,英伟达通过“投资换生态”将业务模式从“硬件销售”升级为“基础设施生态掌控”,OpenAI则获得千亿级资金及优先芯片供应,双方耦合关系已超越简单供需,成为全球AI霸权争夺的核心支点。 从产业链协同看,合作构建了分层锁定的全球化网络:软银参与Stargate计划提供资本支持,微软Azure仍为技术合作伙伴(但部分工作负载迁移至甲骨文OCI),英伟达则作为“preferred strategic compute and networking partner”深度介入OpenAI的AI工厂扩张。这种“美国主导、多方参与”的模式,可能重塑AI云服务市场格局,推动算力资源从“云厂商垄断”向“生态联盟共享”转型。 双方 CEO 均强调此次合作对 AI 技术演进的战略价值。英伟达创始人黄仁勋指出,“这标志着部署 10 吉瓦算力为下一个智能时代赋能”,而 OpenAI CEO 山姆·奥特曼(Sam Altman)则明确表示,“计算基础设施将成为未来经济的基础”。 从技术路径看,10GW 算力中心将支撑千亿级参数模型的训练与推理,推动 AI 实现更复杂的多模态理解、长上下文交互及自主决策能力;从产业影响看,合作模式为 AI 行业树立了资本与硬件捆绑的新范式,模型公司与芯片公司通过利益共同体对冲技术迭代风险,预计将加速 AGI 研发与规模化应用落地。

芯查查资讯

芯查查资讯 . 2025-09-23 3 2825

产品 | 南芯科技车规PMIC家族再添新成员,发布ASIL-D功能安全等级的SBC

今日,南芯科技(证券代码:688484)推出全新 ASIL-D 功能安全等级的车规级 SBC SC6259XQ,可应用于 12V 和 24V 系统,单芯片集成多达 7 路电源,具备完善的输出保护机制及看门狗和 FCCU 功能。SC6259XQ 基于自主知识产权,产业链全国产化,可应用于域控制器、智能座舱和 ADAS 等汽车模块,SC6259XQ 的电源/逻辑功能具备上百种可配置的选项,可以为客户提供更泛化通用的高集成度电源解决方案。 汽车智能化的关键电力支持 SBC (System Basis Chip) 对实现汽车智能化至关重要,作为高度集成的计算平台,SBC 能提供高性能处理器、大容量内存以及丰富的接口,确保车辆在行驶过程中实时处理辅助驾驶等复杂任务,做出快速准确的决策。同时,SBC 能显著节省 PCB 面积、延长汽车电池使用寿命、降低静态电流和系统成本。据预测,2030 年全球 SBC 芯片市场规模将突破 550 亿美元。 SBC 需要管理多个电源轨,为不同器件提供高效稳定的电源,还要具备故障检测和保护功能,确保系统高可靠性。南芯科技凭借在电源领域的深厚积累,重磅发布符合 ASIL-D 功能安全等级的 SBC,可适配不同电压的系统平台,实现高达 7 路输出,为高级辅助驾驶等系统提供高性能的国产化选择。 单芯片高度集成 SC6259XQ 采用 8mm*8mm QFN-56 封装,单芯片集成 5 个 DC-DC 转换器和 2 个 LDO,集成的 DC-DC 转换器包括 1 个同步高压降压控制器 (VPRE),1 个带有集成低端开关的异步低压升压转换器 (LVBOOST),以及 3 个低压降压转换器 (LVBK)。通过高度集成化的设计,大幅降低了 PCB 上电源组件的面积。南芯提供 SC6259XQ 的标准化参考设计,无需手动优化噪声、时序、动态、软件初始化等,设计复杂度低,降低开发周期。SC6259XQ 可支持 I2C/SPI 配置,与 MCU 协同管理电源策略。 高可靠全国产产业链 SC6259XQ 按照 ISO26262 ASIL-D 功能安全流程开发,符合 AEC-Q100 Grade 1 标准,支持逻辑内建自测 (LBIST) 和模拟内建自测 (ABIST),以验证安全逻辑和模拟监测的正确功能,并可通过 32 位 SPI 或 40 位 I2C 接口进行设备控制,提供 PGOOD、复位、失效安全输出和中断功能以用于诊断。为了实现更好的抗 EMC 性能,SC6259XQ 还集成了频率同步、展频、压摆率控制和频率微调等功能。 SC6259XQ 输出带载能力更高,输出电压可配置范围更大。该产品基于公司自主知识产权,产业链全国产化,助力主机厂加速开发周期,提升终端产品竞争力。 多功能灵活应用 SC6259XQ 提供不同数量的 LVBK、FCCU 功能和不同数量的 VMONx 通道选项,具备多种电压监测功能,可配置简易或挑战型看门狗,带有故障恢复策略的 FCCU 监测功能以及外部集成电路监测功能。SC6259XQ 带 2 个唤醒输入引脚 (WAKE1/2);具备模拟多路复用器 (AMUX),供 MCU 实现冗余监控;同时可与其它 PMIC 做上电同步,便于系统拓展。 南芯科技车规级产品家族 南芯科技汽车解决方案面向未来绿色和智能的出行方式,涵盖智能驾驶、车身控制、智能座舱和车载充电等应用,致力于为客户推出一站式芯片解决方案。我们扎根于客户研发场景,基于客户应用不断进行定制设计迭代,帮助客户在汽车核心应用领域更快地设计出效率更高、集成度更高、安全性更高的产品。

南芯科技

南芯科技 . 2025-09-23 1385

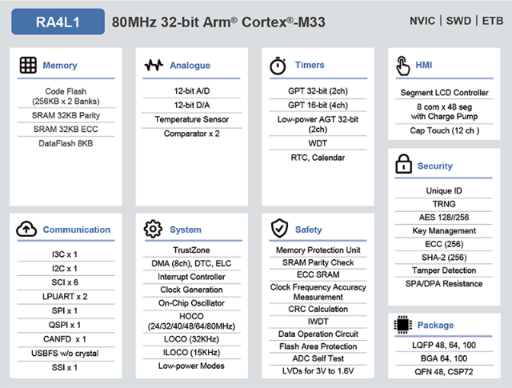

技术 | 您的MCU能否为低功耗设计带来高级安全性?

随着自动化和IoT成为我们日常生活的一部分,高级安全性在低功耗设备中变得更加重要,以确保建筑物安全、阻止入侵者进入家中并保护用户免受任何数据修改或泄漏。 RA4L1 MCU旨在为低功耗设备带来更高的安全性。RA4L1采用瑞萨电子先进的低功耗工艺技术,支持低至1.6V的低工作电压,同时在保留16KB的 SRAM情况下提供低至1.65μA的低待机电流。具有浮点单元(FPU)和TrustZone®的80MHz Arm® Cortex-M33®内核包括支持段码式LCD和高级安全引擎等功能,以支持需要保护其应用和通信的各种低功耗系统。 RA4L1提供512KB的片上双区闪存,具有块交换功能,可轻松实现应用程序现场更新,以及8KB的数据闪存,允许代替外部EEPROM进行数据存储。 最重要的是,RA4L1具有64KB的片上SRAM,支持奇偶校验和ECC,适用于关注数据完整性和安全性的应用。 该产品组提供七种不同的封装,包括LQFP、QFP、BGA和CSP选项,尺寸仅为3.64mm x 4.28mm。这些封装选项使RA4L1对许多空间有限制的应用具有吸引力。 RA4L1框图 RA4L1支持丰富的外设功能,这些功能已针对低功耗应用进行了优化,具有广泛的通信接口,以及丰富的模拟和系统功能。 RA4L1的关键特性之一是段码LCD控制器,这在智能电表和智能恒温器等低功耗应用中经常需要。它设计目的是在RA4L1的最低功耗模式下运行,同时能够驱动多达384段码的LCD。 以下是段码LCD控制器的简化框图和显示每个封装中可用段码数的表格。 简化段码LCD控制器的实现 RA4L1封装类型上的最大LCD信号数量 随着新的网络安全法规和总体安全性的重要性日益增加,为了保护数据和安全通信,每个应用程序在未来都需要更仔细地考虑安全性,而强大安全IP (RSIP)旨在帮助您做到这一点。RA4L1实现了广泛的高级安全功能,包括: RSIP-E11A安全引擎 密钥包装 安全密钥注入和更新 设备生命周期管理(DLM)状态 身份验证和保护级别 安全的工厂编程 Arm TrustZone 篡改检测 可锁定的闪存 RA4L1安全功能的核心是RSIP安全引擎,它是MCU内的一个隔离子系统。安全引擎受到访问管理电路的保护,该电路在发生非法外部访问尝试时关闭加密引擎,防止差分故障分析等攻击。加密引擎包含用于对称和非对称加密算法的硬件加速器,以及各种哈希和消息身份验证代码。安全引擎内是MCU硬件根密钥的一个组件,用于存储和注入其他密钥,我们稍后将看到。它还包含一个真随机数发生器,具有符合SP800-90B标准的熵源和NIST认证的DRBG算法。 RSIP-E11A安全引擎图 安全引擎包含内部RAM,用于处理敏感材料(如纯文本密钥)的操作。此RAM无法在安全引擎之外访问。RSIP安全引擎可以与Renesas灵活配置软件包(FSP)中的更高级别安全结构相结合。FSP是一个增强的软件包,旨在为使用任何RA Arm微控制器的嵌入式系统设计提供用户友好、可扩展、高质量的软件,确保整个系列的软件兼容性。FSP中实施的嵌入式驱动程序和安全原语为嵌入式数据保护和身份识别提供了完整的解决方案。 RA可扩展性强的配置软件包(FSP) | Renesas瑞萨电子 https://www.renesas.cn/zh/software-tool/ra-flexible-software-package-fsp 这些功能使RA4L1非常适合需要低功耗运行、多种通信功能、LCD显示驱动,尤其是安全功能的广泛应用,包括: 音响系统 门禁系统 消费品 工业和公用事业计量应用 安全系统 智能锁 工业传感器 更多信息 有关更多信息,包括文档和视频,请访问RA4L1产品页面。要了解有关如何从概念到生产保护产品的更多信息,包括认证和软件列表,请访问IoT安全页面。 RA4L1 - 基于80MHz Arm Cortex-M33并支持TrustZone、段码LCD控制器和高级安全功能的低功耗MCU | Renesas瑞萨电子 https://www.renesas.cn/zh/products/ra4l1 瑞萨电子的物联网安全解决方案 | 安全连接器件 | Renesas瑞萨电子 https://www.renesas.cn/zh/key-technologies/security/iot-security

瑞萨

瑞萨嵌入式小百科 . 2025-09-23 660

产品 | 安世发布带功能安全的12/16/24通道线性LED驱动器系列产品

安世半导体近期推出了12/16/24通道、每通道100mA驱动能力的线性LED驱动系列产品。该系列产品集成芯片级ASIL-B功能安全,满足车灯系统针对功能安全日渐增加的高要求,非常适用于车外照明中的转向灯、刹车灯、贯穿式尾灯,以及日间行车灯等信号灯和装饰灯。 产品特点 全系列包含12CH、16CH、24CH产品 AEC-Q100 Grade 1认证,功能安全ASIL-B版本可选 每通道支持100mA最大输出电流,支持通道间并联输出 +/-5% 输出电流精度 支持模拟和PWM调光 UART over CAN接口,最多支持27个slaves 集成CAN收发器版本可选 产品优势 全系列支持 ASIL-B 功能安全等级 NEX13XX0-Q100全系列产品提供QM以及ASIL-B版本。 ASIL-B版本芯片可以大幅简化系统安全设计和认证过程。 集成丰富的故障诊断功能 NEX13XX0-Q100全系列产品支持通道开路、短路,以及单颗LED短路等检测功能,在正常工作模式与失效安全模式(fail safe)下均可正常运行,保障系统可靠性。 更低的dropout电压,芯片温升更低 NEX13XX0-Q100系列具备比竞品更低的压差电压(dropout voltage),在同等输出电流条件下,可显著降低芯片输入端 LED 供电电压 VS(~200mV@100mA),从而有效降低芯片功耗与温升。 NEX13120 Competitor1 Competitor2 图1.相同负载,安世产芯片表面温度低8~6摄氏度 优秀的EMI性能 NEX13XX0-Q100系列产品通过优化电路和版图设计,系统EMI性能优异。其传导发射(电压法/电流法)及辐射发射测试结果均以大余量通过CISPR 25 Class 5标准。 支持NTC,实现灵活温度监测 NEX13XX0-Q100 芯片集成了 NTC 热敏电阻输入接口,客户可根据系统需求灵活配置温度监测功能,有效节省 MCU 资源。 典型应用 本系列产品适用于车外照明中的转向灯、刹车灯、贯穿式尾灯,以及日间行车灯等信号灯和装饰灯。 NEX13XX0-Q100全系列支持UART over CAN接口,且12/16/24通道器件的数据帧结构相互兼容,在单一总线架构下,可支持多达27片不同通道数的芯片级联,满足客户对通道数量的灵活配置需求。 图2.三种不同通道数芯片级联方案 产品选型 安世全系列车规级多通道车尾灯LED驱动芯片现可申请样品。客户可根据项目需求灵活选用最合适的芯片设计系统。

安世

安世半导体 . 2025-09-23 8097

产品 | 联发科天玑9500芯片正式发布

9月22日下午,联发科正式发布新一代旗舰移动平台天玑9500。 天玑9500采用台积电第三代3nm制程(N3P工艺),集成超过300亿个晶体管,搭载Arm全新架构,首次推出“第三代全大核”CPU设计,由1颗主频高达4.21GHz的C1-Ultra超大核、3颗3.5GHz的C1-Premium大核及4颗2.7GHz的C1-Pro能效核组成,配备16MB三级缓存和10MB系统缓存,显著提升数据处理效率。 性能方面,天玑9500在实验室环境下实现单核跑分4007,较前代提升32%;多核跑分达11217,提升17%。得益于先进的制程与架构优化,其在峰值性能下超大核功耗降低55%,多核整体功耗下降37%,实现强劲性能与出色能效的平衡。 GPU方面,天玑9500集成最新的G1-Ultra MC12图形处理器,引入GPU Dynamic Cache架构,图形性能提升33%,功耗降低42%。在144Hz高帧率游戏场景中,可实现全程满帧稳定运行,配合“天玑星速引擎倍帧技术3.0”,兼顾高帧率与低功耗表现,光线追踪渲染性能也实现翻倍提升。 天玑9500还首发支持4通道UFS 4.1闪存标准,AI性能同样大幅升级,搭载双NPU架构与“生成式AI引擎2.0”,支持端侧运行大模型,实现文生图、文生文、4K超分等高阶AI功能,响应速度更快且保障用户隐私。 联发科同步推出第二代天玑调度引擎,涵盖超级内存压缩、一致性引擎、算力调度与动画流畅等多项技术,优化系统底层资源调度,确保应用启动、触控响应与动画切换的流畅体验。

MTK

手机中国 . 2025-09-23 4705

企业 | AI时代安全能力如何保障?安谋科技给出核芯IP答案

随着人工智能(AI)技术深入千行百业,安全能力已成为AI规模化落地不可或缺的基石。《关于深入实施“人工智能+”行动的意见》中也明确强调“提升安全能力水平”,进一步凸显了安全在AI产业发展中的核心地位。 安谋科技Arm China打造了从入门级到高性能的完整安全IP产品线——“山海”SPU,提供从芯片IP层到云端的全链路安全防护,广泛覆盖边缘AI、AI基础设施及智能汽车等多个关键领域。 图:安谋科技Arm China 自研“山海”SPU产品家族 边缘AI领域:“山海”SPU E10/E20安全方案主要面向物联网loT设备通用MCU,支持Arm Cortex®-M类微控制器系统;S12安全方案侧重于智能物联网AIoT设备,支持Arm Cortex-A/R类应用处理器系统,可广泛用于智能手机、平板、智能电视、安防、云端设备、网络设备、无人机等行业领域。 智能汽车领域:E20F和S20F提供汽车功能安全,为智能汽车“芯”安全构建提供全面保障。 AI基础设施领域:安谋科技即将推出的新一代“山海”产品,针对AI基础设施的安全升级需求,从硬件IP、软件中间件到云端服务,构建覆盖芯片底层至应用层的全栈安全防护体系,为云计算、网络通信、数据中心及AI应用提供多维防护。 基于这些安全IP产品线,安谋科技Arm China不仅能为客户提供软硬件一体的安全技术防护,同时能协助客户顺利完成安全认证。 在近日举办的Arm Unlocked 2025大会上,安谋科技高级技术总监吕达夫分享了公司面向边缘AI领域的安全产品解决方案,以及多个协助客户获得安全认证的真实案例。 图:安谋科技Arm China 高级技术总监吕达夫发表演讲 安谋科技面向边缘AI领域的系列安全解决方案有三大技术亮点: 1.搭载核心模块TrustEngine,这是一款密码算法引擎,不仅支持国际通用算法,还全面兼容中国商用密码算法,可灵活适配客户多样化的安全需求。 2.原生集成Arm® TrustZone®等核心安全能力,完美匹配各类Arm CPU,能帮助客户显著提升适配效率,降低开发成本与风险,缩短产品上市周期。 3.打造隔离可信的执行环境,保障敏感数据与业务安全。 目前已有多家企业依托“山海”SPU方案成功通过认证。例如,博通集成旗下的Wi-Fi蓝牙双模芯片BK7236凭借该方案获得PSA Certified Level 2认证;欧思微的UWB芯片U101A1C9也在“山海”E20的支持下成功取得国家商密L1认证,为物联网与移动设备领域的安全需求提供了坚实支撑。 从边缘AI到智能汽车,到AI基础设施,安谋科技将持续推动安全技术与计算效能协同进化,为AI时代构建坚实可信的安全基石。

边缘AI

安谋科技 . 2025-09-22 1130

- 1

- 4

- 5

- 6

- 7

- 8

- 500