产品 | 艾迈斯欧司朗推出面向创新汽车设计的新一代氛围灯解决方案

中国 上海,2025年10月20日——照明与传感创新的全球领导者艾迈斯欧司朗(SIX:AMS)今日宣布,艾迈斯欧司朗OSIRE™ E3030凭借约0.5瓦级的光输出,成为车辆设计中兼具功能性和美学性的关键要素。该器件具备可靠结构,通过抗振动设计与温度波动耐受性验证,符合汽车标准认证体系,尤其适用于光信号作为交互媒介且可视性要求严苛的场景,包括自适应信号系统及人机交互系统(HMI)。此外,OSIRE™ E3030也非常适用于钢琴漆或实木饰面等高吸光性装饰材料的背光照明,支持隐形式发光设计。 随着汽车内饰设计日益成为差异化竞争的关键,光源在塑造现代座舱的设计语言与创意空间方面发挥着决定性作用,其挑战在于:如何在延长光效覆盖距离的同时,确保在日间依然清晰可见。因此,应用于汽车内饰光源的光输出能力亟待提升。 为应对这些高标准挑战,艾迈斯欧司朗推出OSIRE™ E3030,实现光输出性能的重大升级。依托精准分档技术,该产品稳定运行于0.5W功率层级。根据选定色坐标,其在200mA分档电流下可实现典型光通量输出,红/蓝光范围为22.4-40流明或7.1-14流明,绿光在150mA分档电流下达28-50流明。丰富的可选波长扩展色域范围,KRTB DSLP31.33系统用户可从中选取最匹配需求的方案。独立可寻址的色彩通道赋予用户色彩选择与混色的最大灵活性。LED芯片的三角形排列确保卓越的角度颜色一致性——这对耦合圆形导光管的光学设计具有决定性优势。 0.6mm的超薄元件高度配合3.0mm×3.0mm紧凑占板面积,使其能够完美适配对元器件空间要求极为苛刻的高端应用场景。 OSIRE™ E3030产品图片 该LED通过AEC-Q102认证,符合汽车行业的高质量标准。其优异的环境耐受性更可拓展至工业及消费领域,助力极端工况下的稳定运行。 艾迈斯欧司朗在彩色LED领域拥有逾1,500项专利资产,凭借行业领先的产品组合为其创新OSIRE™产品提供技术保障。 OSIRE™ E3030即日起开放订购。

氛围灯

艾迈斯欧司朗 . 2025-10-20 1060

技术 | 智能制造中,如何为物理AI挑选传感器?

智能制造是数字技术与传统制造流程深度融合的体现。其中的核心是物理人工智能 (AI),它将 AI 算法引入物理系统,例如机械臂、自动引导车辆 (AGV) 和计算机数控 (CNC) 机床。物理系统要能有效运行,离不开来自物理环境的实时数据,而传感器的作用正在于此。 工业传感器扮演着“眼睛和耳朵”的角色,在现代制造和自动化领域中已成为不可或缺的基石,从基础的测量设备蜕变为能够全方位监测离散自动化与过程自动化的精密系统。当与 AI(视觉 AI、声学 AI 或物理 AI)相结合时,工业传感器让物理系统具备了自学习能力,进而助推制造效率、安全性的提升,并促进数字孪生技术和数据分析的应用。本文将深入探讨各类传感器及其应用。 洞悉工业传感器及其工作原理 工业传感器是感知和处理各种物理参数的器件,如距离、压力、温度、流量、液位、运动、速度、加速度等。它们收集的数据,对于监测和控制制造流程而言,可谓举足轻重。收集到的数据随后会通过数字/模拟输入输出 (I/O) 及通信模块发送到可编程逻辑控制器 (PLC) 或 CNC。 在典型的工业传感器中,主要组件(见图 1)包括传感元件、电压基准源、运算放大器 (OpAmp)、模数转换器 (ADC)、处理器、接口和电源管理模块。传感元件负责测量物理参数,并将其转化为电压、电流、电阻等电信号。 图 1. 典型工业传感器的组成模块 工业传感器充当着 AI 与物理世界之间的接口,恰如人体中的神经系统。当数字世界需要与物理环境进行交互时,离不开模拟和混合信号传感器。下一代工业自动化系统不仅在信息技术 (IT) 云端融入 AI 能力,还将 AI 嵌入到部署在现场的操作技术 (OT) 器件中。换言之,AI 算法将应用于边缘端的传感器或可编程逻辑控制器 (PLC)/机器人中,以实现快速决策。 在此,我们将重点探讨工业自动化中所使用的传感器。 传感器类型 图像(视觉)传感器: 图像传感器借助摄像头拍摄在制产品的图像和视频,以此判断产品的有无、方位及精度,是质量控制与检测环节中不可或缺的器件。图像传感器凭借单个装置即可实现对产品多个点位的检测,为机器视觉提供有力支撑。安森美 (onsemi)的图像传感器和短波红外摄像头兼具低功耗和出色的图像质量,具备高动态范围和低光性能,助力系统在各类智能工厂场景中均发挥出理想效能。 图 2. 机器视觉系统框图 位置和扭矩传感器: 尽管霍尔效应传感器、力传感器和光学传感器已应用于电机位置控制,但考虑到磁体、精密电阻等感应元件及光学编码器复杂的制造工艺,整体方案的成本实则居高不下。 如今,一种新趋势逐渐兴起:在运动控制和机器人技术相关应用中开始采用电感式位置传感器,以带绕组的印刷电路板 (PCB) 作为感应元件,并搭配模拟前端 (AFE) 和控制器。NCS32100和 NCV77320两款产品相较传统位置传感器具有专门优势,包括但不限于耐温性强、机械结构简化、抗污染能力出色等。 超声波传感器: 超声波传感器借助超声波来测量距离,非常适合检测透明物体(不同于光学传感器),且不受灰尘和污垢的影响。安森美的 NCV75215是一款性能出色的接近传感器,检测距离为 25 厘米至 4.5 米。在自主移动机器人中,超声波传感器用于导航和避障;在过程自动化应用中,可对流体进行流量与液位检测;而在成品质量检验中,可用于识别缺陷与裂纹。 光电传感器: 光电传感器借助光线实现物体检测,分为对射式、反射式和漫反射式三种类型,各自具备不同的特性和应用场景。光电传感器以非接触检测、适用几乎所有材料、支持长距离视距检测为显著优势,主要采用红外与激光技术。安森美的 QR1113是一款性能优良的反射式传感器,940 纳米红外发射器与配套的硅光电晶体管并排封装,提供表面贴装和通孔两种封装形式。 接近传感器: 接近传感器基于电磁感应原理,可在无物理接触的情况下检测金属物体,且对灰尘、油污等环境因素具有极强的耐受能力。若需检测非金属物体,则以超声波和光电技术为优选方案。 压力传感器: 压力传感器应用于气动、液压或洁净室环境中,用于维持理想运行状态并对偏差发出警报。它们通常以应变片或力敏电阻为核心,采用惠斯通 (Wheatstone) 电桥结构来抵消误差,通过微小电压变化实现压力测量。 温度传感器: 温度传感器用于监控和调节温度,应用范围覆盖食品加工、机械运行等多个行业。常用类型包括热电偶、电阻温度检测器 (RTD) 及半导体温度传感器,例如安森美的 ADM1023。 环境传感器: 气体传感器、化学传感器等环境传感器,用于在需要保持警惕的环境中监控特定的有毒或易燃气体,常常集成在安全系统中。例如,NCV76124雨量和光线传感器最初为汽车应用设计,可通过光电二极管发射并测量反射光,进而识别环境中的颗粒物。再如,用于连续血糖监测 (CGM) 的 CEM102 电化学传感器模拟前端与 RSL15 蓝牙 5.2 微控制器配合使用时,能在极低的系统功耗下实现对化学电流微小变化的测量。 传感器的主要考量因素 为智能制造中的物理 AI 系统挑选适配传感器时,需重点关注以下五大因素: 应用所需的精度与速度:传感器必须满足特定AI 任务对精度和速度的要求,例如实时质量检测、预测性维护、机器人控制等任务。 数据质量与可靠性:传感器会随着时间推移生成海量数据,而AI 可对海量数据进行分析以挖掘其中的规律。能够持续提供可靠数据的传感器,对于训练和运行 AI 模型至关重要,可为整个制造生态系统中的敏捷决策奠定坚实基础。 互操作性与集成:传感器应当能与现有制造系统无缝集成,并支持标准的现场总线和通信协议。换言之,新型 AI 传感器必须具备小型化特性且能够实现互操作。 网络安全与数据隐私:随着联网传感器数量增多,网络威胁风险也在增高,对OT 和IT 安全的要求愈发严苛。确保边缘数据传输的安全至关重要,尤其是当 AI 系统依赖传感器提供的敏感操作数据进行决策时。为此,可采用具备自校准和冗余功能的传感器,用于检测和隔离威胁。 可持续性与能效:在为物理AI 系统扩充传感器数量时,操作人员仍需将功耗控制在预算范围内,而具有低工作电流的传感器在系统扩展性方面具备显著优势。 综上,工业传感器是物理 AI 系统的基本构成要素,使物理 AI 系统能够在边缘与云端对真实世界进行感知、理解和交互。随着 AI 的不断演进,传感器技术的进步将成为充分释放 AI 潜力的关键,助力智能制造领域开发出更智能且适应性更强的系统。安森美在智能传感技术领域具有优势,凭借丰富的传感器产品组合与深厚的应用专业知识,正走在助力客户向工业 5.0 转型的前列。

智能制造

安森美 . 2025-10-20 855

技术 | Arm 出席 OPPO 开发者大会,解读端侧 AI 技术与应用新趋势

10 月 15 日,OPPO ColorOS 16 发布会暨 OPPO 开发者大会在深圳隆重召开,大会现场除发布 OPPO 最新技术外,还举办了多场论坛,与业界领袖共同探讨科技创新与人工智能 (AI) 新生态构建。在大会上,Arm 受邀发表了主题演讲,分享端侧 AI 的演进趋势及 Arm 最新的 Lumex AI 计算平台如何助力技术突破、应用创新及生态合作。 端侧 AI 实现“从可选到必需”的跃迁,个性化成核心方向 “仅一年时间,端侧 AI 就已从‘可选功能’变为用户‘基础期待’。”Arm 终端事业部智能手机市场高级总监 Steve Raphael 在演讲中指出,2024 年行业还在探讨端侧 AI 的落地可能性,2025 年实时智能就已成为移动设备的“必需品”。AI 不仅能力更强,也变得更具“个性化”,能为每个人提供专属服务。 这种转变的核心在于快速演进的用户“个性化”需求与 AI“主动协作”能力。依托大语言模型 (LLM) 与智能体 AI (agentic AI) 的发展,当前端侧 AI 已经可以自主完成推理、规划与任务执行:从梳理工作流、实时翻译,到预判用户潜在需求,甚至主动生成旅行方案、会议纪要,整个过程丝滑流畅。这种更懂用户的“无感化智能交互”,正是端侧 AI 的终极目标。 SME2 + KleidiAI 技术,加速端侧 AI 性能优化 如今,智能手机已成为端侧 AI 的核心入口,深度承载着用户生活、工作中的海量任务。与此同时,智能系统对“即时响应、随时可用、隐私安全、低功耗”的需求日益迫切,传统计算模型在应对这类实时化、个性化的智能诉求时,已逐渐显现出适配短板。为助力合作伙伴突破行业挑战、匹配产业发展核心需求,Arm 最新推出“AI 优先”的 Lumex 计算平台。该平台通过硬件、软件及工具等层面的协同创新,帮助开发者更高效地实现端侧 AI 功能突破,最终为智能手机用户带来更优质的体验升级。 硬件层面,作为智能手机的智慧中枢,CPU 在端侧 AI 中发挥着关键作用,得益于其强大的“通用计算”特性,开发者更倾向于将工作负载保留在 CPU 上,仅将真正需要的部分迁移到其他硬件。Arm Lumex 计算平台搭载了 Arm 最新 C1 系列 CPU——也是首批基于 Armv9.3 架构的 CPU 系列产品。作为 Lumex 平台最亮眼的技术之一,SME2 技术为 C1 CPU 带来颠覆性提升:处理 AI 工作负载的速度较前代提升 5 倍,能效提升 3 倍,在耗时低于 100 毫秒的轻量任务中,其性能甚至超越了传统 GPU。值得关注的是,SME2 技术在实现性能突破的同时,并未增加开发者的技术适配门槛,反而有效降低了端侧 AI 功能的开发与落地成本。 软件层面,Arm 于 2024 年推出了 KleidiAI 轻量级软件,这是一款面向 AI 框架开发者的轻量级内核库,能够在无可比拟的规模下,为广泛的技术市场以及各类基于 Arm 架构的设备——从早期搭载 Neon 技术的设备到最新 Lumex 平台——提供 AI 模型和工作负载的无缝性能优化。目前,KleidiAI 已集成至所有主流移动操作系统及 AI 框架中,包括 PyTorch ExecuTorch、谷歌 LiteRT、阿里巴巴 MNN 及微软 ONNX Runtime,并已在 Android 与 iOS 系统中广泛应用。借助 KleidiAI,开发者无需修改任何代码,即可自动取得 SME2 的加速能力,为 Arm 生态中 2,200 万开发者提供高效便捷的端侧 AI 开发支持,并显著降低技术应用门槛与开发成本。 此外,Arm Lumex 平台通过“自顶向下”的方法和工具,帮助开发者快速定位不同 CPU 的性能问题,实现跨平台的一致体验优化。 支付宝、淘宝等应用率先落地,解决端侧 AI 真实用户痛点 对开发者而言,技术最终要落地到实际应用场景。演讲中,Steve Raphael 分享了 SME2 技术在国内应用场景的落地案例,印证了端侧 AI“从技术到价值”的转化路径。在支付宝应用中,SME2 为“回忆视频”功能提供强大的支持,可自动将用户相册照片生成为动态视频集锦;在淘宝应用场景下,SME2 助力实现“端侧实时电商重排序”,通过 LLM 精准匹配用户偏好,同时支撑“拍照购物”功能——用户拍下商品图片后,可即时检索同款,大幅缩短购物链路。 此外,Arm 与谷歌合作优化 Android AICore 组件(赋能 Gemini Nano 模型),将智能回复等功能的安全模型延迟降低 20%;与 Stability AI 联合开发的 Stable Audio Open 音频生成模型,通过 CPU 混合浮点与整数数据处理的优势,在手机端实现“文本生成音频”,且功耗远低于 GPU 方案。 与生态伙伴协同创新,端侧 AI 进入“共生时代” 端侧 AI 的下一个阶段,已不是性能参数的比拼,而是生态协同的较量。Arm 的技术探索始终以“开放协作”为核心,与硬件、软件和应用领域的生态伙伴紧密协作,充分释放端侧 AI 在实际场景中的应用潜力,其中与 OPPO 的合作便是业界典范。目前,Arm 已与 OPPO 深度合作,将 SME2 技术集成至 OPPO 的 AI 框架中,在显著提升 AI 性能优化和开发效率的同时,有效降低了 OPPO 生态开发者的技术门槛。 SME2 已在端侧 AI 领域产生了实际影响——无论是性能还是准确率,都实现了显著提升。目前,Arm 正积极将 SME2 技术扩展至每一个 CPU 平台。预计到 2030 年,SME 与 SME2 技术将为超过 30 亿台设备新增超 100 亿 TOPS 的计算能力,持续降低端侧 AI 的部署成本与隐私风险。回应 OPPO 开发者大会“共建 AI 新生态”的理念,Steve Raphael 表示,Arm 将持续以 SME2、KleidiAI 等技术为支点,与生态伙伴携手,推动端侧 AI 从“单点创新”走向“生态共生”,最终让端侧 AI 体验惠及每一位用户。

AI

Arm . 2025-10-20 880

德明利亮相GITEX Global,以智能存储加速全球化布局

2025年10月13日,全球科技盛会GITEX GLOBAL 2025在阿联酋迪拜世界贸易中心开幕。本届展会聚焦人工智能驱动数字化转型,德明利携全栈定制化消费级存储产品与解决方案亮相,以创新存储技术为全球高性能计算提供关键底层存储支撑,通过深化产业链合作,实现从“走出去”到“融进去”的跨越发展,助力全球人工智能生态构建。 中东“芯”机遇,AI驱动消费电子新蓝海 全球存储市场正迎来由AI驱动的重要升级周期。据CFM闪存市场最新预测,2025年全球存储市场规模合计高达1932亿美元,将创下历史最高记录。AI相关存储应用需求持续旺盛,消费电子成为增长动力:AI手机推动LPDDR5X内存显著提升,AI PC带动DRAM单机容量提升向24GB迈进,QLC NAND技术的普及更加速1TB成为高端设备的标配。 中东地区凭借其数字经济潜力,为存储产品创造新增量空间。该地区坐拥连接亚、欧、非三大洲的区位优势,依托沙特“2030愿景”、阿联酋“人工智能战略”等国家级政策对科技产业的高额投资,推动数字化转型全面提速。同时,中东地区年轻化的人口结构(50%人口年龄低于25岁),推动高端电子产品需求持续增长,为中国存储企业提供了技术输出与产业链协同的重要机遇。 全栈定制解决方案,智能化产品适配多元场景 随着AI向端侧设备渗透,德明利针对中东市场推出低功耗、高性能的智能存储产品矩阵,持续升级OEM存储解决方案,全面覆盖AI PC、电竞与移动创作场景。 三大消费级产品驱动智能化体验升级 固态硬盘:高速接口全覆盖,满足AI PC与内容创作场景 德明利支持PCIe 4.0 / 5.0接口标准,读取速度最高达12000MB/s,容量达4TB,全系搭载智能温控与动态功耗管理,适配中东地区高温环境,稳定支持AI计算、高帧率游戏与4K渲染。 内存条:DDR5高性能系列,推动电竞与AI终端体验升级 DDR5内存条容量最高达96GB,支持一键超频技术,频率可达10000+MHz,以低延迟高带宽提升AI多任务与电竞场景性能,并通过主流平台认证,保障高负载稳定运行。 移动存储:全场景便携方案,助力跨设备内容创作 PSSD移动固态硬盘读取速度达2000MB/s,具备抗震结构与宽温适应能力;MicroSD卡搭载自研主控芯片,支持智能缓存管理与动态功耗控制,满足无人机、运动相机在高温多尘环境下的可靠存储。 从“走出去”到“融进去”,实现存储产业链共赢发展 产品与渠道并进,构建本地化服务能力 在全球化战略推进中,德明利正从“产品出海”迈向“生态落地”,依托智能制造基地与研发中心,积极推进本地化渠道与服务网络建设,为客户提供快速响应、贴合需求的一站式服务。 探索本地化合作模式,推动技术共赢 基于“芯片-固件-场景”全流程能力,德明利持续深化与中东企业在固件定制、技术认证等环节的合作,推动产业链环节区域落地,着力推动“服务融进去”与“技术走上去”,以研发实力与服务体系树立高端存储市场的品牌形象。 未来,德明利将持续深耕中东市场与做好产业链协同发展,为后续拓展全球高潜力市场奠定基础。

德明利

德明利 . 2025-10-20 1 2150

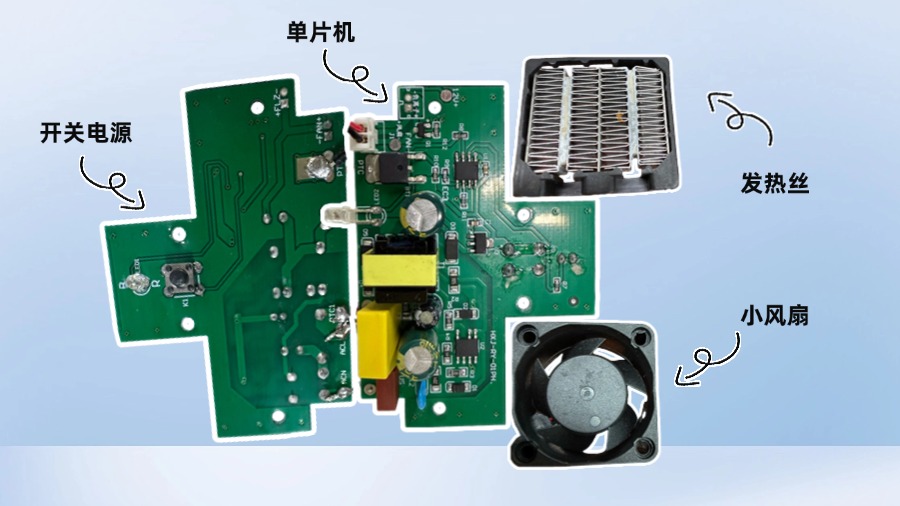

阴雨天出差也能晾好衣!纳祥科技烘干衣架方案可拆卸设计,双温干衣提速50%

针对传统晾晒受天气影响、干衣机体积大,以及梅雨天/阴雨天/潮湿环境衣物鞋子难干、异味滋生等问题,纳祥科技为客户打造了一款便携式可拆卸烘干衣架方案,方案无遮罩设计,三向出风,即插即用,支持30℃柔风护衣与60℃强力速干双模式。 (一)方案概述 本方案通过单片机接收用户指令(物理按键选择30℃/60℃模式),以PWM信号调节发热丝功率,并同步驱动风扇,形成定向热风流。三组独立风道实现立体循环送风,加速衣物干燥及杀螨除菌。 方案采用单片机+小风扇+发热丝+开关电源的极简架构,具备60dB低噪音及150W低功耗(仅0.2度电/小时)特性,低音运行,适配各类烘衣、烘鞋的场景需求。 (二)功能模块 ①主控单元:以单片机为核心,处理按键输入、温度控制及状态指示(LED灯) ②加热模块:发热丝搭配散热片提升热效率 ③送风系统:微型风扇,优化风压与噪音 ④电源管理:开关电源模块,具备过热保护功能 ⑤机械结构:可拆卸风管,支持快速拆装清洗 (三)方案演示 下面是本方案演示—— ①开机后按键蓝光闪烁 ②再按切换:红灯为60°热风模式,蓝灯为30°暖风模式 (四) 方案总结 本方案以低成本、高灵活性为核心,采用双温模式覆盖全场景需求,通过三向送风提升效率,并配备可拆卸结构便于收纳,适用于家庭、宿舍、差旅等多种场景。 我们现将提供完整的方案技术支持与迭代,欢迎您与我们深入交流与探讨。

纳祥科技

深圳市纳祥科技有限公司微信公众号 . 2025-10-20 1 2520

工业视觉网关:RK3576赋能多路检测与边缘AI

在工业4.0与智能制造的推动下,产线对检测效率、良率与可追溯提出了更高要求。传统IPC方案在通道数、功耗、体积与集成成本之间难以平衡,尤其在 AOI(自动光学检测)、装配工序监控、不良品溯源 等环节,企业既要“看得更清”,也要“判得更准、追得更全”。 RK3576 工业视觉网关的差异化价值: 12路 1080P@30fps 并发采集H.264/H.265 硬件编解码端到端延迟约 120~150ms6TOPS NPU 边缘AI推理易对接 MES / 追溯系统 一、产线痛点:从“人看”到“机判”的转变 · 多工位/多角度同步:单机位覆盖不足,典型项目需 8~12 路并发,且画面时序一致性要求高。 · 实时性与稳定性:漏检/误检带来返工与投诉风险,系统需长时稳定、低时延。 · 质量追溯与合规:检测结果需与工单/MES/条码绑定,形成可回溯的证据链。 · 成本与部署:希望以更低功耗/体积/成本替代传统IPC+独显的组合。 二、方案核心:多路检测 + 编解码 + 边缘AI + MES对接 多路并发采集 RK3576 提供 3×4-lane MIPI-CSI,配合视频转换模块可并发接入 12路 1080P@30fps。前端 RGA 做尺寸/色彩统一,减少后端负载。 高效硬件编解码 内置 VPU 支持 H.264/H.265,显著降低带宽与存储压力;结合 RTSP 实现低延迟内网推流,便于大屏与质检台查看。 边缘AI推理 6TOPS NPU 支持缺陷检测(焊点/丝印/划伤)、尺寸测量、异常动作识别等模型,先筛后存,减少云侧负载。 MES/追溯集成 通过工单/条码绑定检测结果与图片片段,输出 检测记录 + 判定标签 + 位置标注,打通 MES/ERP/追溯 流程。 三、典型落地场景 · AOI自动光学检测:多角度对比 + 边缘AI判定,降低 DPMO,提升 FPY。 · 工序/装配监控:对漏装/错装/姿态异常进行实时识别与拦截,减少返工。 · 不良品剔除与取证:与分拣机构联动,自动剔除并生成可追溯证据。 · 设备远程诊断:多路画面聚合上墙或远程回传,辅助专家快速定位问题。 与传统 IPC 方案对比(概览) 维度 RK3576 边缘网关 传统IPC+独显 通道并发 12路1080P@30fps(优化可扩) 受PCIe/采集卡限制,成本上升 功耗/体积 低功耗、小尺寸,边缘部署友好 功耗高、体积大、散热复杂 集成成本 SoC一体化,软硬件链路短 多卡多驱动,系统复杂度高 AI扩展 内置NPU,近端推理 需独立推理卡或云端依赖 说明:以上为工程经验参考,实际指标视镜头、光学与算法复杂度而定。 四、价值总结 基于米尔 RK3576 的工业视觉网关,将 “多路检测 + 硬编硬解 + 边缘AI + MES集成” 融为一体:在保障画质与时延的同时,显著降低系统复杂度与总体成本,并以数据闭环驱动良率持续提升。 想了解更多关于米尔RK3576核心板/开发板的详细信息? 欢迎访问我们产品页面:https://www.myir.cn/shows/151/81.html

工业视觉网关

原创 . 2025-10-20 4080

产品 | 江波龙推出业内首款集成封装mSSD,Office is Factory实现灵活、高效交付

10月20日,江波龙基于“Office is Factory”灵活、高效制造的商业模式,推出集成封装mSSD(全称“Micro SSD”)—— 通过重构常规SSD介质的定位与形态,打造出“高品质、高效率、低成本、更灵活“的SSD新品类,进一步创新了SSD的商业应用灵活性,并提升了用户参与感与创造性体验。目前,这项创新产品已完成开发、测试,并申请了国内外相关技术专利,处于量产爬坡阶段。 mSSD是通过特定的封装工艺,将控制器芯片/存储芯片(Die)、无源元件(电阻、电容等)以及不同功能的集成电路集成在一个封装体内,实现它们之间的电气连接、物理保护与热管理。这一创新不仅提升了生产效率、降低了生产管理成本,更推动了存储介质的商品化,实现了一站式的灵活交付。 集成封装:芯片级质量 mSSD采用Wafer级系统级封装(SiP),一次性把主控、NAND、PMIC等元件整合进单一封装体内,这一设计将原本PCBA SSD近1000个的焊点减少至0个,规避了PCBA生产工艺中可能出现的阻焊异物、撞件隐患、高温高湿、腐蚀性等可靠性问题,尤其适用于M.2 2242、M.2 2230这类PCBA空间有限的形态。 集成封装将SSD从PCBA质量等级提升至芯片封装质量等级,从而将≤1000 DPPM降低至≤100 DPPM,全面提升产品质量。 精简制造流程:实现降本增效 mSSD通过开创性设计,极大简化了PCBA分离式SSD的复杂生产流程。与传统方式需先将Wafer在不同工厂完成NAND、控制器、PMIC等元件的封装测试,再转运至SMT工厂进行排产贴片不同,mSSD完全省去了PCB贴片、回流焊等多道SMT环节及各站点转运,实现了从Wafer到产品化的一次性封装完成,将交付效率提升了1倍以上,进而使整体Additional Cost(附加成本)下降超过10%,构筑更具竞争力的综合成本优势。 此外,面向对低碳环保有较高要求的客户,mSSD的生产流程直接避免了SMT环节中的高能耗工序,从而显著降低了能源消耗与碳排放,使单位产品碳足迹得到有效控制,能够充分满足客户的绿色环保需求。 强效散热:满速长效运行 集成封装大幅压缩了mSSD的体积,使其实现20×30×2.0 mm的尺寸与2.2 g的重量,实现轻薄化。在紧凑空间内,通过深度技术优化,其性能仍能满足PCIe Gen4×4接口的高标准。实测数据显示,该产品顺序读取速度最高可7400MB/s;顺序写入速度最高可达6500MB/s;4K随机读取速度最高可达1000K IOPS;4K随机写入速度最高可达820K IOPS,整体性能表现稳定,适用于PC笔电、游戏掌机扩容、无人机、VR设备等场景。 mSSD采用高导热铝合金支架、石墨烯贴片与强导热硅胶,构建高效散热系统,同时保持轻薄体型,可广泛兼容超薄设备。凭借创新散热结构,mSSD峰值性能维持时间达到行业领先水平,满足各类高负载应用需求。此外,在功耗表现上,产品亦符合行业标准,满足NVMe协议L1.2≤3.5mW的低功耗要求,同时峰值(Peak)功耗也符合协议规范。 未来,这套高效散热技术将持续提升,为高性能PCIe Gen5 mSSD做好散热技术储备。 灵活扩展:SKU多合一 mSSD在形态创新的同时,充分保障客户端兼容性。产品搭载TLC/QLC NAND Flash,提供512GB~4TB多档容量选择,并创新性地配备卡扣式散热拓展卡,无需工具即可灵活拓展为M.2 2280、M.2 2242、M.2 2230等主流规格,实现SKU多合一,灵活适配不同类型的应用需求。 相较于部分SSD方案存在的接口非标准、SKU数量多、兼容性弱,或是on board类型产品不易于维护等情况,mSSD集成封装设计让客户扩展、替换SSD更便捷,维护成本也随之降低,在综合适配性与使用效益上,更能匹配当下多样化的存储应用需求。 此外,产品供应到客户端后,即可通过彩喷/UV打印机等设备完成产品定制化信息喷绘,并随时随地完成组装和零售包装,切实落地“Office is Factory”的高效、灵活制造商业理念,让客户端无需投入高昂的成本,便可快速实现SSD的生产与个性化定制。 共创价值 赋能品牌创新机遇 未来,mSSD将以其“集成封装、灵活制造”的通用优势,同时赋能行业类与消费类品牌客户,满足市场对快速定制、可靠质量、紧凑交付与成本控制的综合要求,并帮助品牌打造差异化产品,构建敏捷响应市场变化的核心竞争力。 随着产品技术制造的持续深化,江波龙将为客户提供更多存储创新,向更广泛的场景延伸。

江波龙

江波龙 . 2025-10-20 2 1435

新品 | 以高性价比赋能汽车与泛能源,纳芯微发布 NS800RT115x 系列实时控制 MCU/DSP

纳芯微正式推出 NS800RT115x 系列高性价比 MCU,基于 Arm® Cortex®-M7 内核,主频高达 200 MHz,搭载自研 mMATH 数学加速核,集成高速 ADC、精细 PWM、CAN FD、增量式编码器接口以及功能安全模块,可高效处理三角函数、反三角函数、开方、滤波等数学运算,大幅提升实时运算效率,可广泛应用于车身电子与照明、电机驱动器、数字电源等领域,提供符合 ISO 26262 ASIL-B 与 AEC-Q100 Grade 1 标准的型号,为汽车与工业控制应用提供高性能与高可靠的解决方案。 高性能内核,构筑实时算力基石 NS800RT115x系列采用 200 MHz Cortex®-M7 高性能内核,内置 8 KB L1-Cache、256KB嵌入式Flash 与总计 80 KB TCM,均支持 ECC 校验,实现核内零等待访问,显著提升实时响应与数据处理效率,为复杂的运行工况提供更高的可靠性。自研mMATH 数学加速核可快速执行三角函数、超越函数、平方根、滤波等复杂运算,为电机控制与数字电源场景提供更强的计算支撑。 NS800RT115x系列选型表 精准控制外设,优化复杂工况响应 NS800RT115x系列继承NSSine™家族高精准增强控制外设,内置两组 12 位 ADC(最高 4.375 Msps、21 通道),配合4组模拟比较器与 14路 PWM 输出(其中4个通道输出最高分辨率可达 80 ps),实现高精度控制,尤其是对异常工况的快速保护响应;丰富的内联关系,能更友好的实现OC/CBC等控制方式,是一款在数字电源、光储逆变、电机控制领域量体裁衣之作。 升级高速互联,赋能车规级通信 NS800RT115x系列在通信接口上实现全面升级,除 UART、SPI、I²C、PMBUS、LIN 等标准外设外,新增 CAN FD 控制器,在保持兼容 CAN 2.0B 的同时,实现更高的通信速率与数据吞吐量,更好地满足车载网络与实时控制系统的高带宽需求。 功能安全可靠,兼顾灵活适用 产品内置总线监控单元(BGCRC)、多级看门狗、时钟与电源监控电路,支持自诊断与异常检测机制。产品的设计符合 ISO 26262与 IEC 61508等功能安全要求,符合 AEC-Q100 Grade1 标准,为复杂汽车与工业应用提供坚实的可靠性保障。 此外,NS800RT115x 系列提供 LQFP80/64/48、QFN32等多种封装,满足从高性能控制单元到紧凑型模块的不同设计需求。 其应用覆盖车身电子与照明系统、电机驱动器、数字电源、光储逆变等泛能源场景,为客户带来高算力、高可靠与高集成度的系统解决方案。 目前,纳芯微已覆盖高、中、入门三大实时控制产品系列,实现了全供应链国产化要求,通过精准设计和供应链协同,在保证实时控制核心性能的前提下,实现成本优化,促进行业长期发展。

纳芯微

纳芯微电子 . 2025-10-20 3 865

企业 | 安世事件让国产化替代更进一步,捷捷IDM,铸就自主可控之路!

近日,中国商务部正式发布公告,为维护国家主权、安全和发展利益,决定对安世半导体(Nexperia)等相关物项实施出口禁令。这一重大举措,是中国在复杂国际环境下为捍卫自身权益的正当、必要反制,同时也为中国半导体产业链敲响了最急促的警钟——核心技术必须掌握在自己手中,供应链安全必须立于自主可控的基石之上。 在此历史性关头,捷捷微电肩负使命,凭借深厚技术积累与完整产品布局,已构建起全面对标并替代安世半导体(Nexperia) 的成熟方案,为保障中国电子产业的连续性与安全性提供坚实后盾。 捷捷微电产品矩阵 全系列精准对标,无缝替换 总而言之,当行业在寻找安世的替代方案时,捷捷微电提供的远不止于此。我们凭借更卓越的产品性能 ,在关键的能效与可靠性指标上实现了对标与超越。安世留下的空白,恰恰成为了验证我们技术实力的试金石。选择我们,意味着您不仅解决了供应链的安全问题,更是在为您的产品注入更强劲的“中国芯”性能。如果您对我们的产品感兴趣,欢迎随时邮箱联系我们muyan@jjwdz.com,也可登录我们的官网www.jjwdz.com进一步了解。 捷捷微电郑重承诺 亲爱的客户与合作伙伴们,请放心。面对外部的风云变幻,我们深知您对供应链稳定的担忧。此刻,我们想郑重地告诉所有曾经使用安世产品的伙伴:捷捷微电成熟的产品矩阵,从性能到品质,皆可实现对安世产品的无缝替代、完美接续。 这不是一次被动的替代,而是一场主动的进击。当某些势力试图以“断供”为刃,划伤中国科技产业的脉络时,我们更应清醒地认识到:真正的安全感,来源于技术的自主与产业链的强韧。此次对安世的限制,正是中国在半导体领域发出的有力回击,也是一次国产芯片走向前台的重大契机。 前路或许仍有挑战,但每一次的“不被卡脖子”,都始于每一次的“敢于替换”。捷捷微电愿与您携手,用国产芯片点亮中国制造的明天。让我们共同扛起这面国产化替代的旗帜,为国家半导体产业的发展,增添一份不容小觑的中国力量。 中国芯,一定行。

捷捷微电

捷捷微电 . 2025-10-20 3520

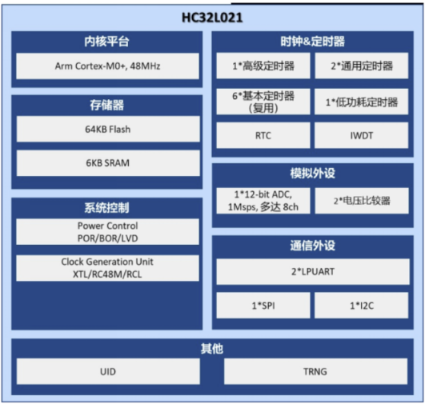

新品推荐 | 小华半导体超低功耗MCU产品HC32L021

功耗,始终是衡量MCU产品竞争力的核心指标之一,尤其是在电池供电的便携设备和长期待机的应用场景中。近期,小华半导体针对低功耗应用推出了一款新的超低功耗MCU产品HC32L021,该MCU采用了Arm Cortex-M0+内核,主频可达48MHz。 攻克超低功耗设计壁垒 既然是为低功耗应用而设计,HC32L021在功耗方面的表现肯定值得肯定。据其数据手册显示,HC32L021在深度休眠模式下,功耗低至0.65µA。在此模式下,所有时钟关闭,但IO状态保持、IO中断有效,且所有寄存器、RAM和CPU数据均能完整保存,确保快速唤醒和任务无缝衔接能力。 即便是在全速运行的48MHz工作模式下,其动态功耗也仅为45µA/MHz。之所以能达到如此功耗表现,是因为小华半导体采用了先进的电源管理技术与国产超低漏电工艺技术相结合的策略,从根本上优化了能耗表现。 图:HC32L021功能框图(来源:小华半导体) 也就是说,HC32L021这款MCU无论是对于需要长久续航的智能家居传感器、医疗设备,还是对能耗极其敏感的货架标签、无线模块等应用,都能显著延长设备的工作寿命,降低运维成本。 不止低功耗,外设也很丰富 除了低功耗这一优势之外,HC32L021在性能和外设方面也配置拉满。其搭载的是业界主流的Arm Cortex-M0+ 32位处理器内核,工作主频可达48MHz,相较于传统的8/16位MCU,它在处理复杂算法、执行多任务时拥有很大的优势,但其成本却与8/16位MCU相当,展现出了极高的性价比。 在存储配置上,该系列MCU配备了64KB的Flash存储器和6KB的RAM,充分满足多样化应用对程序空间和数据缓存的需求。更值得一提的是,其高度集成的丰富外设资源,使其成为一个功能全面的“多面手”。 定时器系统:集成了1个支持三相带死区互补PWM输出的高级定时器(ATIM3),2个可灵活配置的通用/基本复合定时器(CTIM),1个低功耗定时器,以及1个支持高精度补偿的实时时钟(RTC),能够轻松应对复杂的电机控制、电源管理和精准计时任务。 通信接口:板载2组LPUART、1组SPI和1组高速I2C接口,为设备间的数据交换和网络连接提供了灵活、可靠的通道。 高精度模拟外设:内置1个12位1Msps采样率的高速高精度SAR ADC、2路电压比较器(VC)和1路低电压侦测器(LVD),使其在传感器信号采集、电池电压监控等模拟应用中游刃有余。 内建安全保障:HC32L021还集成了真随机数发生器(TRNG),为需要安全加密的应用提供了硬件级支持,同时每颗芯片拥有全球唯一的10字节ID号。 另外,在可靠性方面,HC32L021从设计之初便遵循工业级标准。它支持1.8V至5.5V的宽电压供电范围,增强了对电源波动的适应性。其工作温度范围覆盖-40℃至105℃,能够从容应对各种极端环境挑战。此外,高达±4KV的ESD_HBM(人体放电模型)防护能力,确保了产品在复杂电磁环境下的稳健运行。 小巧封装与完善生态:加速产品创新落地 为了适应现代电子产品小型化、集成化的趋势,HC32L021系列提供了包括TSSOP20、QFN20(3x3mm)以及尺寸仅为2x2mm的QFN14等多种超小封装选项,为工程师的紧凑型设计提供了极大的便利。 图:小华半导体HC32L021系列产品具体型号及参数(来源:小华半导体官网) 在开发支持方面,小华半导体提供了完善的生态系统。开发者可以获取HC32L021的STK基础款和MINI开发板,以及配套的驱动库样例SDK。同时,小华编程器及ISP工具也已全面支持该系列芯片,配合Keil、IAR等主流IDE,可帮助用户快速上手,显著缩短产品开发周期,加速创新应用的商业化进程。 结语 随着半导体制造工艺的进步和市场竞争的加剧,入门级32位MCU正以前所未有的价格优势和性能优势,加速替代传统的8/16位产品。小华半导体HC32L021的推出,无疑是这一市场变革中的一个重要里程碑。它凭借在超低功耗、核心性能、外设集成度和工业级可靠性等方面的卓越表现,完美契合了智能家居、医疗设备、电机控制、安防报警等众多领域的核心需求。 有关HC32L021系列样片申请、开发板购买及技术支持,可以联系中电港,或小华半导体及其他授权代理商。

小华半导体

芯查查资讯 . 2025-10-20 13 1 3595

中国台湾省晶圆厂最新布局与产能统计(2025版)

重点内容速览: 1. Foundry晶圆厂在中国台湾的分布 2. IDM晶圆厂在中国台湾的分布 中国台湾省虽然地方不大,但却主导着全球半导体的生产。据波士顿咨询公司与半导体行业协会的数据,中国台湾省生产了全球约60%的芯片,以及超过90%的先进芯片。可以说,其晶圆制造能力,特别是先进制程制造能力独步全球。 通过数据统计可以发现,中国台湾省的晶圆制造业呈现出四大特点,即业务模式高度集中(以纯晶圆代工为主)、IDM厂商不多(主要集中在存储和功率器件领域)、地理分布高度聚集(主要集中在台湾西部的三大科学园区,近年高雄和嘉义也被纳入选址范围),以及技术迭代和产能扩张持续进行。 图:中国半导体产业分布热力图(来源:芯查查 SaaS ) 与我们前面两篇介绍美国和中国大陆的晶圆厂一样,我们分别从IDM和Foundry两个类别来介绍台湾省的晶圆厂最新分布情况。 IDM晶圆厂分布 与中国大陆的情况有些类似,台湾省的IDM厂商也并不发达,主要包括华邦电子(Winbond)、旺宏(Macronix)、南亚科、华亚科和瑞晶等存储器IDM企业,以及强茂(Powerchip)、台半(Tatung Semiconductor)等功率器件IDM企业。 在存储市场,今年第二季度以来,DDR4价格大幅上涨,7、8月份现货市场一度出现了翻倍行情。9月份起,服务器用的DDR4需求也开始变大,带动了PC与消费类DDR4报价同步上行。另外,近期NAND Flash的报价也开始走高。而这些都是中国台湾省的优势产业,特别是三星、美光等企业逐步退出了DDR3和DDR4产品的生产,华邦电子与南亚科技成为了支撑DDR4市场的关键力量。 华邦电子成立于1987年,总部位于台湾省中部科学园区,在存储领域已经深耕30多年。初期专注于DRAM和NOR Flash技术研发,此后还推出了NAND Flash产品,但主要还是专注在中低容量存储产品。如今华邦电子有两座晶圆厂,制程主要以成熟制程为主,比如已经推出了24nm的Flash产品、20nm的DRAM产品,该公司还计划2025年下半年推出16nm DRAM产品。华邦电子的两座晶圆厂均为12英寸,分为位于台中市大雅区中部科学园区和高雄市路竹区南科高雄园区。其中高雄厂正从25nm升级到20nm制程,第一产能1.5万片/月,将扩充DDR4与特殊应用产品供应。台中厂的产能为5.7万片/月。 此外,针对今年来逐渐兴起的边缘AI应用,华邦电子推出了CUBE(定制化超高带宽软件),目前该产品主要在高雄厂进行试产,多数将采用16nm制程,也有少数客户采用20nm制程。 旺宏电子成立于1989年,总部位于台湾省新竹科学园区。该公司可以提供跨越广泛规格及容量的ROM、NOR Flash,以及NAND Flash存储器解决方案。其主要业务是Flash(NAND和NOR)、ROM和晶圆代工服务。它们拥有1座6英寸晶圆厂(Fab1)、1座8英寸晶圆厂(Fab2)、1座12英寸晶圆厂(Fab5),以及1座测试厂,是少数具备IC设计、生产制造、测试及销售的IDM厂商。不过最新的消息是,2025年9月11日,旺宏宣布将其竹科的6英寸晶圆厂以28亿元新台币(约6.48亿元人民币)的价格出售给东京电子。 产能方面,Fab2的产能约为4.5万片/月,主要生产NOR Flash,也有部分产线用于晶圆代工业务;Fab5的产能约为5万片/月,约不足1万片用于NOR Flash,其余用于生产NAND Flash和ROM产品。 南亚科技是全球第四大DRAM企业,市占率在3%左右。通过先后与日本冲电气、IBM、英飞凌、奇梦达、以及美光合作,加上自主研发,将DRAM制程从0.32μm提升至10nm。 目前,南亚科技将10nm技术分为A、B、C、D四代。2021年,其10nm级1A技术已经试产成功,2022年在新北市新建一座12英寸工厂,计划投资3,000亿元新台币,兴建一座双层式无尘室新厂,并在该晶圆厂导入数代10nm级技术与产品。新厂规划分三个阶段,完成后月产能可达4.5万片晶圆。 产能方面,目前南亚科技的产能约为6万片/月,已经完成了旧产线升级到1B/1Cnm制程,可稳定供应DDR4和利基型DRAM产品。 另外,美光也在中国台湾省布局了两座12英寸晶圆厂,分别是位于桃园科学园区的林口厂(Fab11)和台中中部科学园区的台中厂(Fab16),不过其内部已经将这两个厂区合而为一,目前已经有最新1β nm制程的投片。 产能方面,Fab11的产能为10.8万片/月,Fab16为10万片/月。此外,美光还在中国台湾省开设了一个新的办公室,收购了友达光电的台中工厂,将其改建为DRAM生产基地,进一步提升DRAM产能。 IDM模式是功率器件企业发展壮大的护城河,中国台湾省排名靠前的强茂、台半均为IDM模式,都有自己的晶圆厂。 国外半导体厂商DIODES通过收购敦南科技,获得了其位于新竹市新竹科学园区的晶圆厂。 图:台湾省IDM晶圆厂分布及产能情况(来源:各公司官网,芯查查) Foundry晶圆厂分布及产能 纯晶圆代工厂占据了中国台湾省绝大多数的晶圆产能,且在全球市场中占据主导地位,这其中尤以台积电(TSMC)为甚。其一家公司的营收就占据了全球代工市场约七成的份额。截至2025年10月,其在台湾省的布局规模庞大,且仍在持续扩张中。当然,除了全球排名第一的台积电,还有联电、世界先进、力积电等也在代工市场占有不少市场份额。 2024年台积电宣布了一个新的概念“晶圆代工2.0(Foundry 2.0)”,台积电将不仅仅提供晶圆制造加工,还提供封装、测试、光罩制作等环节。到目前为止,其Foundry 2.0计划已经取得一定成绩,最新的2025Q3财报显示,先进封装的营收占比在持续上升,战略地位也日益重要。 根据其官网信息,台积电在台湾省运营着4座12英寸晶圆厂、4座8英寸晶圆厂和1座6英寸晶圆厂。不过最新的消息是台积电已经准备逐步停止6英寸晶圆生产业务,并整合8英寸产能,提升效率。 具体来看,台积电的晶圆厂高度集中在台湾省西部的三大科学园区,形成了强大的产业集群。 新竹科学园区(Hsinchu Science Park) :这是台积电的总部所在地和发源地。园区内不仅有多座晶圆厂,如晶圆二厂、三厂、五厂、八厂、十二厂等,还设有全球研发中心。晶圆十二厂(Fab 12)是其重要的12英寸研发和生产基地。 南部科学园区(Southern Taiwan Science Park) :位于台南市,是台积电先进制程的生产重镇。例如,晶圆十四厂(Fab 14)和晶圆十八厂(Fab 18)均坐落于此。其中,晶圆十八厂是3纳米制程的主要生产基地。 中部科学园区(Central Taiwan Science Park) :位于台中市,同样是台积电12英寸产能的重要组成部分,例如晶圆十五厂(Fab 15)即位于此。 产能方面, 基于以上晶圆厂,截至2024年底,台积电及其子公司所拥有及管理的年产能超过1,600万片12英寸晶圆当量,仅4座超大12英寸晶圆厂的年产能就超过了1,274万片。台积电也在8英寸晶圆领域发力,SEMI数据显示,2024年全球8英寸晶圆厂月产能达690万片(全年约8,280万片),其中台积电占约7.2%(以600万片/年估算)。 近几年来,台积电也在全球积极布局产能,规划了数座12英寸晶圆厂,其位于中国台湾省的两座12英寸晶圆厂在2025年开始量产,分别是位于新竹市的Fab20和高雄市的Fab22,这两座工厂将是2nm的量产基地。两座厂皆于2022年动土兴建,并计划于今年开始投入生产。此外,台中的Fab25厂将于2025年底开始兴建,2028年量产A16,或比2纳米更先进的技术。 联电是台湾省第二大、全球排名前列的纯晶圆代工厂,它在全球拥有12座晶圆厂,包括4座12英寸晶圆厂、7座8英寸晶圆厂和1座6英寸晶圆厂。其总部位于台湾省新竹科学园区,在台湾的晶圆厂主要分布在: 新竹科学园区(Hsinchu Science Park) :作为公司总部,园区内拥有多座8英寸晶圆厂。 南部科学园区(Southern Taiwan Science Park) :位于台南市,是其最先进的12英寸厂Fab 12A的所在地,专注于28纳米及更先进制程的生产。 联电位于台南市的Fab12A已于2002年进入量产,可量产14nm制程产品。目前产能超过8.7万片/月。 图:联电晶圆厂布局(来源:芯查查SaaS) 世界先进有台积电拆分而来,专注于8英寸晶圆代工,在特殊工艺领域,比如电源管理IC、驱动IC拥有重要地位,其晶圆厂主要分布在台湾省新竹和桃园。 其晶圆一厂(Fab1)是世界先进的创始厂,早期以DRAM生产为主,2004年转型为逻辑代工;晶圆二厂(Fab2)是2008年收购自华邦电子的8英寸晶圆厂,初期以存储芯片为主,后逐渐转向逻辑代工;晶圆三厂(Fab3)是2014年收购自南亚科技的8英寸晶圆厂,并整合了胜普电子设备;晶圆五厂(Fab5)则是2022年收购的友达光电L3B厂房。产能方面,2025年的所有晶圆厂年产能等效8英寸晶圆345万片(包括台湾的4座8英寸晶圆厂和新加坡的一座8英寸晶圆厂产能)。 力积电的业务模式比较特殊,既生产自有的DRAM产品,也提供存储器和逻辑芯片的晶圆代工服务。 该公司拥有4座12英寸晶圆厂和2座8英寸晶圆厂,主要厂区位于新竹科学园区。每月可提供等效8英寸晶圆40万片。其位于苗栗县铜锣的12英寸晶圆厂Fab P5的第一期工程已经完成,且已于2024年5月开始量产,主要生产55nm和40nm制程芯片,当前月产能约1万片。第二期工程P6预计2029年投产,可生产55nm、40nm,以及28nm制程芯片,预计月产能可达4万片。 图:Foundry晶圆厂在中国台湾省的布局(来源:芯查查,各公司官网) 另外,新唐科技是2008年从华邦电子分离出来的,目前以自有逻辑IC产品制造、销售为主,晶圆代工为辅的公司。该公司可以提供6英寸晶圆代工服务,其晶圆厂源自华邦电子6英寸晶圆厂,位于中国台湾省新竹科学园区内,月产能约4.5万片。目前可提供0.35μm以上工艺,包括逻辑、混合信号、高压、超高压、电源管理、Mask ROM、嵌入式闪存,以及定制化工艺(比如IGBT、MOSFET、TVS、压力传感器等)产品代工服务。 结语 截至2025年10月,台湾的晶圆制造产业展现出由“纯晶圆代工”模式绝对主导的格局。以台积电为首的代工巨头不仅在台湾的新竹、台南、台中科学园区部署了庞大的现有产能,更通过在高雄、嘉义等地兴建新厂,积极布局2纳米及以下的未来尖端技术。这一系列投资确保了台湾在全球半导体供应链中的战略核心地位。 总体来看,台湾晶圆厂的未来发展将继续围绕技术领先、产能扩张和产业集群深化这三大主轴,持续引领全球半导体制造业的走向。

晶圆厂

芯查查资讯 . 2025-10-20 5 2 7460

产品 | 英飞凌推出采用TO-247PLUS-4回流焊封装的CoolSiC™ MOSFET 1400V G2系列

【2025年10月17日,德国慕尼黑讯】电动汽车充电、电池储能系统,以及商用、工程和农用车辆(CAV)等大功率应用场景,正推动市场对更高系统级功率密度与效率的需求,以满足日益提升的性能预期。同时,这些需求也带来了新的设计挑战,例如,如何在严苛环境条件下实现可靠运行,在应对瞬态过载时如何保持稳定性,以及如何优化整体系统性能。为应对这些挑战,全球功率系统和物联网领域的半导体领导者英飞凌科技股份公司(FSE代码:IFX / OTCQX代码:IFNNY)推出采用TO-247PLUS-4回流焊封装的CoolSiC™ MOSFET 1400V G2系列。该器件支持更高的直流母线电压,可实现更优异的热性能、更小的系统尺寸,以及更高的可靠性。 采用TO-247PLUS-4回流焊封装的CoolSiC™ MOSFET 1400V G2系列 该封装技术支持在260°C温度下进行多达三次回流焊操作,并可在结温高达200°C的条件下实现可靠运行,同时确保出色的峰值电流能力。借助英飞凌.XT互联技术,这些器件在严苛的应用环境下,依旧可实现更优的热性能以及更强的机械可靠性。全新1400V电压等级为更快的开关速度提供了额外裕量,并简化了过压保护措施。这有助于降低对功率降额使用的需求,同时提升整个系统的可靠性。 采用TO-247PLUS-4回流焊封装的CoolSiC™ MOSFET 1400V G2,其导通电阻(RDS(on))等级涵盖6至29毫欧(mΩ),适用于对高功率密度要求严苛的应用场景,例如商用、工程和农用车辆(CAVs)、电动汽车充电以及电池储能系统。英飞凌还提供采用高爬电距离TO-247-4封装的 CoolSiC™ MOSFET 1400V系列。该产品组合的RDS(on)等级范围为11至38mΩ,其器件同样适用于光伏等应用场景。

英飞凌

英飞凌工业半导体 . 2025-10-17 1 1265

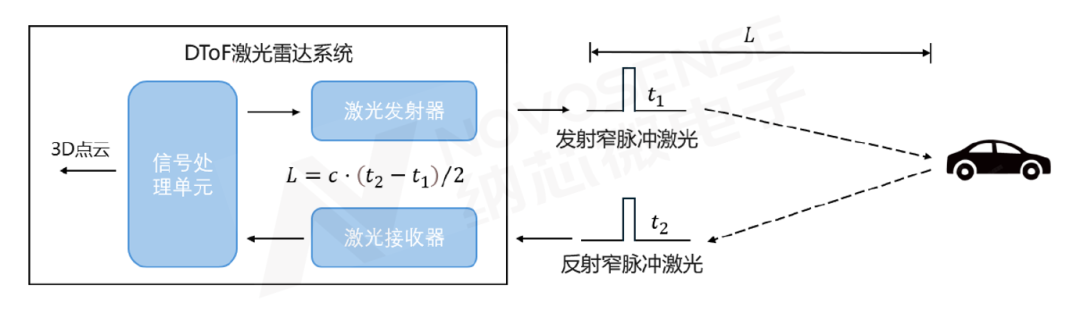

技术 | 从原理到布线:GaN栅极驱动Layout实战,解锁激光雷达性能跃迁

激光雷达(Lidar)是一种用于精确测距的激光探测技术。栅极驱动器与GaN器件在最大化激光器发射能力上起到重要作用,为激光雷达带来更高的分辨率。NSD2017是一款适用于激光雷达应用的驱动器,具有强驱动能力、支持极窄脉宽输出以及强抗干扰能力的特点。本文从激光雷达的应用特点出发,介绍NSD2017在应用中PCB设计的注意点。 激光雷达技术概要 汽车自动驾驶中的激光雷达常采用DToF(Direct Time-of-Flight)测距方式,即通过直接测量激光的飞行时间进行距离测量和地图成像。图一是DToF激光雷达系统的典型结构,信号处理单元通过记录激光发射器发出光脉冲的时刻,以及激光接收器收到光脉冲的时刻,根据时间间隔和光速就可以计算出目标距离。 图1 DToF激光雷达系统典型结构 为实现高分辨率和宽监测范围,需要极窄的激光脉冲、极高的激光脉冲功率以及极高频开关频率,对激光发射器中的功率器件提出了较高的要求。相较于传统的Si MOSFET,GaN器件的快速开关速度以及高脉冲电流能力,非常适合DToF的应用,而GaN器件则需要对应的栅极驱动器进行驱动。以图2典型应用电路为例,低侧驱动器NSD2017驱动GaN器件为激光器提供高峰值电流。其中,激光脉冲越短,电流斜率要求越高,对PCB寄生电感的要求越高。本文从优化驱动回路出发,给出了NSD2017的PCB Layout建议。 图2 典型激光雷达驱动电路 驱动回路设计要点 为减小栅极驱动回路寄生电感对驱动性能的影响,首先需要分析驱动器NSD2017开通和关断GaN器件的回路。图3给出了栅极驱动回路的示意图。 图3 栅极驱动回路示意图 红色曲线为驱动开通回路,当NSD2017输入信号转为高电平时,去耦电容正端经驱动器内部PMOS、驱动电阻至GaN HEMT的栅极,再由GaN HEMT的源极经地平面回到去耦电容负端。蓝色曲线为驱动关断回路,当NSD2017输入信号转为低电平时,电流经GaN HEMT栅极、驱动电阻、驱动器内部NMOS,再经驱动地平面回到GaN HEMT源极。 栅极回路电感的主要影响有以下几个方面:1)栅极回路电感直接影响开关性能,降低有效栅极驱动速率;2)栅极回路电感与GaN器件栅极电容形成谐振回路,将在GaN器件栅极产生过电压;3)谐振产生的驱动信号将导致器件误开关,这对低阈值电压的GaN器件影响尤为严重。 为减低寄生电感和器件栅极电容谐振的影响,一般会在驱动器输出增加驱动电阻,NSD2017分裂式输出的特点便于根据驱动开通和关断的谐振表现,灵活调整电阻阻值RG1和RG2。虽然调整驱动电阻可以解决驱动开关过程中遇到的振铃或误开关问题,但减缓了驱动开关速度,从而影响流经GaN HEMT的电流斜率,因此解决开关振铃的最好方法还是减小寄生电感。以此角度,可以从减小栅极回路电感和减小共源电感两个方向出发。 回路寄生电感设计要点 以驱动开通回路为例,栅极回路的寄生自感可以认为由两部分组成:其一是由去耦电容至驱动器VDD引脚的寄生电感LVDD、驱动器封装电感LN、驱动输出电感LG1和LG、GaN栅极封装电感组成,寄生电感大小与旁路电容、栅极驱动器和GaN的相对位置以及PCB的走线长短粗细有关;其二是由GaN源极封装电感、GaN源极PCB电感LSRC以及地回路电感LGND组成,受GaN封装设计、地回路的处理以及过孔的放置等影响。 为减小驱动回路电感,有两个方向: 其一是减小驱动回路走线自感。建议使用短粗走线进行连接。由于面积相同的情况下,长走线的寄生电感大于细走线,长走线宽度增加一倍时,走线电感并不会减半。因此GaN器件与驱动器的相对位置摆放尤为重要。以下图为例,GaN器件栅极紧靠驱动器输出,驱动开通电流路径(蓝色)与返回电流路径(灰色)实现层间平行。 图4 驱动器与GaN器件摆放 与栅极关断回路相比,开通回路的寄生电感的减小,还需要考虑电流流过高频去耦电容带来的影响。一般建议在NSD2017靠近供电引脚VDD附近放置大、小容值的两个电容,大容值电容一般为1-2uF用于保持VDD稳定,小容值电容一般为100nF-500nF用于滤除高频噪声。小容值电容使用短粗连线靠近放置VDD引脚附近,如果允许的话,建议使用低自感瓷片电容,如馈通电容等。 其二是合理利用磁通抵消原则减小寄生电感。比较简单的方式是,观察驱动开通电流路径和返回路径所围面积,面积越小,寄生电感越小。因此,电流返回路径选择开通电流路径紧邻的层,可以最大限度增加电感耦合实现最小化电感。 共源电感设计要点 栅极驱动电流路径和功率回路电流路径共用器件源极的寄生电感,这部分电感称为共源电感,一般由GaN 器件源极封装电感和源极PCB电感两部分组成。 共源电感同样需要最小化,且在激光雷达应用中最小化共源电感的优先级高于最小化栅极回路电感。当器件开通和关断过程中,共源电感在开关时刻产生与栅极驱动电压相反的电压,将减缓器件的开关过程,增大开关损耗,影响GaN的电流斜率,从而影响光脉宽信号。 为减小共源电感对驱动性能的影响,常利用开尔文连接方式将驱动回路和功率回路分开,以减小耦合。目前有商用GaN 器件中集成开尔文引脚,实现栅极电流回路与功率电流回路的解耦,消除了共源电感的影响。 图5 器件集成开尔文引脚以消除共源电感影响 而目前较多低压GaN 器件没有开尔文引脚,可以通过PCB处理将功率回路和驱动回路分开。常见的处理方式如图6所示,选择靠近器件栅极的源极引脚作为驱动回路,其他引脚作为功率回路。 图6 利用封装分开驱动回路和功率回路 为实现最小共源电感,功率地与驱动地之间单点连接,建议将微过孔尽量靠近驱动器和功率器件摆放,如图7所示。 图7 建议的微过孔摆放方式 图8给出NSD2017一种常见的Layout设计,GaN器件中靠近Gate的Source中放置微孔,实现驱动地与功率地的单点连接,同时选用驱动开通电流相近层作为电流返回层,实现回路面积最小。(示例Layout仅2层,用作说明) 图8 NSD2017推荐Layout

纳芯微

纳芯微电子 . 2025-10-17 7 2720

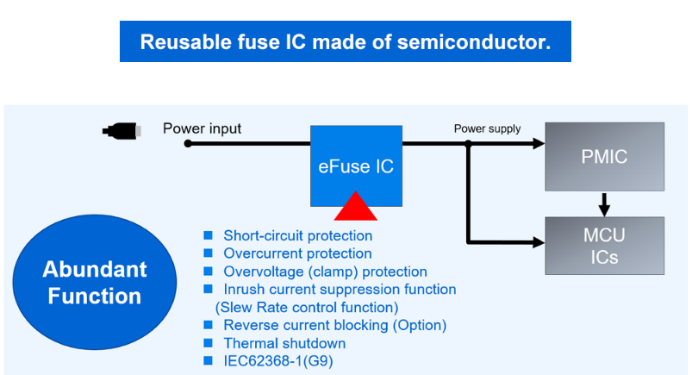

技术 | 认识eFuse IC,智能保险丝为电器保驾护航(一)

芝识课堂的全新内容又和你见面了。从本期开始,我们将用四节课为大家系统介绍半导体保险丝(eFuse IC)的相关知识。内容包括eFuse IC的基本概念、与传统保险丝的性能对比、典型应用示例以及其丰富的保护特性,例如过流保护、短路保护、过压保护和转换速率控制等。让我们一起了解这颗智能芯片如何为现代电子设备提供更可靠的保护。 什么是eFuse IC? eFuse IC是一种基于半导体技术的可复位保护器件。它采用集成电路工艺,将多种高性能、高精度的保护功能集成于单一封装中,具备可重复使用、响应速度快和功能丰富等优点。这不仅有助于降低系统的维护成本,也大幅缩短了故障后的恢复时间。 eFuse IC具备自动恢复和外部控制两种主要工作模式。例如在过热保护(TSD)后,自动重试型eFuse会在条件恢复正常时自主导通;而锁存型eFuse则需要通过外部控制信号重新触发才能继续工作。这种灵活性使其可适应多种复杂应用场景。 eFuse IC优势何在? 不同于传统的玻璃管或片式保险丝,eFuse IC不再依靠金属熔断来切断电路,而是通过内部控制电路实时监测电流与电压,并借助功率MOSFET实现快速关断。由于其不会因一次故障就永久失效,因此极大地提高了系统的可维护性和长期使用的经济性。 除了可复位这一突出优点之外,eFuse IC还具备高精度的过流和短路保护能力,响应速度远优于传统可恢复保险丝。此外,它通常还集成过压保护、反向电流阻断和浪涌抑制等功能。尽管单颗eFuse IC的体积可能略大于普通保险丝,但由于省去了大量外围保护元件,其总占板面积反而可能减小,有利于系统集成。 从综合成本角度看,虽然eFuse IC的单价高于传统保险丝,但其集成多种保护功能、无需更换、符合最新安全标准等特点,可显著降低后续维护与认证成本,因此更适用于对可靠性和安全性要求较高的电子产品。 目前,东芝的eFuse IC产品线非常多,包括TCKE805NA、TCKE805NL、TCKE812NA、TCKE812NL、TCKE800NA、TCKE800NL、TCKE712BNL等。这些产品全面符合国际安全标准IEC 62368-1的要求。该标准基于“安全工程”理念制定,涵盖多项严苛测试,如持续短路、过流及过载运行等。使用通过认证的eFuse IC有助于整机产品减少认证难度、加快上市周期。 总之,eFuse IC作为一种新型电路保护器件,具有精度高、功能多、可复用和符合新安全标准等优势。它不仅提升了系统的可靠性,也在整体成本方面展现出显著价值。

eFuse

东芝半导体 . 2025-10-17 1 1355

方案 | Supermicro推出数据中心建构组件解决方案的全新业务线,提供数据中心设备与管理服务

Supermicro推出数据中心建构组件解决方案的全新业务线,提供数据中心设备与管理服务 业界首个一站式数据中心解决方案,可实现更快的启动上线时间、卓越的性能,和更低的成本 涵盖关键计算、电源、冷却设施、管理软件,和数据中心相关服务 液冷式模块化建构组件可依据客户的工作负载与部署环境,进行优化配置 数据中心层级、机柜层级,以及预验证的计算集群,皆于出货及部署前依据客户规格进行数据中心规模的工厂测试 【2025年10月14日加州圣何塞讯】Super Micro Computer, Inc.(NASDAQ:SMCI)作为AI/机器学习、HPC、云端、存储和5G/边缘领域的全方位IT解决方案供应商,宣布其数据中心建构组件解决方案(Data Center Building Block Solutions®,DCBBS)正式上市。这些解决方案作为Supermicro的全新业务线,可让企业透过单一供应商完成数据中心的完整设计、采购与建置程序,进一步缩短启动上线时间(Time-to-Online,TTO),以及提升整体质量与维护效率。Supermicro解决方案现已涵盖完整的数据中心IT基础设施,包括服务器、存储、管理软件、液冷设施、网络及其他电子组件等,且所有组件在出货前皆在Supermicro制造基地内进行整合与测试。透过此项完整IT解决方案,企业可直接与Supermicro合作,进而简化整座数据中心的建置流程。 Supermicro总裁兼首席执行官梁见后表示:「基于我们为全球多家大型数据中心营运商提供解决方案的专业与经验,我们意识到,提供完整的IT基础设施解决方案,将能助力企业简化数据中心的建置流程。我们的全球制造团队已准备好,依据特定的数据中心需求,为客户提供现代化、高能效数据中心建置项目的一切必要IT组件,以及完整的数据中心管理软件。透过这项全新业务线,我们的服务可加速完整数据中心的建置与部署。此外,我们的液冷解决方案专为最新一代GPU、CPU及其他电子组件设计与优化。与现有的气冷式数据中心相比,Supermicro液冷技术与设施组件可使数据中心耗电量减少最高40%。 核心DCBBS组件 Supermicro数据中心建构组件解决方案的主要组件包括: AI与计算系统 多元类型的高密度、高效率及高扩充性优化系统。这些系统结合了NVIDIA、AMD与Intel的最新AI与加速计算技术,并具有多种机型规格以支持各类计算工作负载。 结合多家软件定义网络(Software-Defined Networking,SDN)合作伙伴技术的Peta级与对象存储服务器。这些服务器专为具有严苛需求的AI工作负载设计,可最大化数据处理量。 由Supermicro内部设计的液冷板,能针对系统内的电子组件,有效移除最高98%的热能。 机柜内(In-Rack)解决方案 提供多种类型的冷却液分配歧管(CDM)与冷却液分配单元(CDU)配置。垂直式CDM可支持更高的服务器密度。Supermicro的In-Rack CDU可提供最高250 kW的液冷性能,并支持最高45 °C的冷却液,同时搭载备用电源供应器与帮浦,以确保稳定性。 后门式热交换器(Rear Door Heat Exchanger,RDHx)可直接安装于服务器机柜后方,有效移除核心组件附近的热能,大幅降低数据中心对空调的需求。 Supermicro以太网络交换器(Ethernet Switch)针对多种计算工作负载进行了优化,可支持最高800 GbE的连接速度与51.2 Tbps的性能。根据客户的需求与喜好,Supermicro也提供合作伙伴的Ethernet、InfiniBand及Omni-Path交换器。 对于整合了AI服务器与交换器的最新一代机柜,机柜式电源(Power Shelf)正成为其中一项必要组件。Supermicro提供33 kW功率/层的机柜式电源,并可适用于各种尺寸的机柜。 电池备援模块(Battery Backup Unit,BBU)架对于企业与关键任务工作负载至关重要。Supermicro BBU可在断电发生时提供48 V直流电、33 kW功率、能持续90秒的备援电力,以支持应用程序完成检查点(Checkpointing)机制,避免应用程序的完全重启。此BBU可被整合至多种机柜配置。 数据中心的成功部署需要高度的机柜通用性。Supermicro提供的机柜解决方案可支持最新液冷式服务器、机柜式电源,以级电池备援模块架。 机柜列间式(In-Row)解决方案 Supermicro列间式CDU可为多组高功率液冷式服务器机柜提供足够的散热性能。这些列间式CDU能够为最高1.8 MW的服务器运行热量进行冷却,并可同时与多个机柜连接。 Supermicro液对气(Liquid-to-Air,L2A)Sidecar为独立运作组件,能将服务器产生的高温冷却液在数据中心内完成冷却,无需对基础设施进行改建就可导入液冷技术。此外,这些Sidecar能对最高200 kW的服务器所产生的热能进行冷却。 Supermicro SuperCluster提供可扩充式的集群单元,并整合了多个机柜与网络架构,是可高度客制化的即插即用(plug-and-play)解决方案。这些系统在出货前皆经过严格的L11或L12验证测试,确保客户能顺利从Pilot Project阶段进展至正式部署,进而扩大AI基础设施规模。 场域基础设施解决方案 数据中心交换器连接与布线是数据中心级解决方案中的核心要素。Supermicro DCBBS提供优化流量工程设计,以及布线技术的完善整合、完整设计与规画文件,包括路由与端口的对应连结(Routing/Port Mapping)和线路长度的优化。此设计与部署服务可缩短启动上线时间、降低材料与人力成本,并提升整体客户体验。针对需要许多系统一起运行,以解决复杂计算问题的工作负载,网络交换器架构也成为了必须的组件。此外,Supermicro也提供了多种高性能、高灵活性与高稳定度的交换器机型,以支持各类应用程序。 Supermicro提供的水冷塔(Water Cooling Tower)具备多种配置,以因应许多类型的数据中心冷却需求。这些水冷塔易于安装,并可多台共同平行运作,以提升整体散热性能。 针对水资源有限的部署环境,Supermicro亦提供干式冷却器(Dry Cooler),能以与水冷塔相同的模块化设计,实现低PUE(电源使用效率)与低 WUE(水资源使用效率)。这些干式冷却器具备绝热辅助式(Adiabatic-Assisted)预冷功能,可在高温环境与各种条件下确保高效散热与稳定运行。 部分数据中心需要配置发电机,而Supermicro的全新发电机产品系列提供从500 kW到3,000 kW的不同功率,并支持快速启动与高度的Step-Load Acceptance,并内建自动电源切换开关(Automatic Transfer Switch)。 变压器可为MW级组件提供稳定、低阻抗的电力,并可选择性启用智能监控与Loop-Feed功能,实现快速、稳固的部署。同时,此系列变压器输出功率可进行配置,支持从750 kVA至5,000 kVA的范围,以因应不同数据中心需求。 管理软件套件 SuperCloud Composer®(SCC)是一套全面的数据中心生命周期管理软件,可监测数据中心内的服务器、网络设备,以及液冷设施。它可在服务器、网络、PDU、CDU、冷却塔,和第三方系统之间,进行一体式的机柜与液冷管理。此软件也具备电源管理、进阶漏液侦测、防护和警示功能,以确保GPU与冷却设施的正常运作。透过大规模式的监测与调校功能,SuperCloud Composer可透过单一连接端管理超过20,000台主机。 SuperCloud Automation Center(SCAC)提供预先建置的企业级自动化技术,涵盖从韧体、操作系统部署,至Kubernetes与AI工作负载启用的完整流程,同时确保极佳的安全性、可扩充性与管理模式。 SuperCloud Developer Experience Console(SCDX)提供一站式且高度的开发者灵活性能,并支持自选式资源分配、AI原生工作流程,以及内建的监测功能,助力团队更快速并安全地从程序代码层面进展至模型开发。 SuperCloud Director(SCD)提供多租用户(Multi-Tenant)AI云端控制功能,可整合裸机计算、以太网络与InfiniBand网络,以及多个存储平台。 服务与现场部署 Supermicro全球服务是全新的专业性服务,同时也是DCBBS的环节之一。此服务提供全面的服务层级组件,包括数据中心设计、解决方案验证及专业现场部署。这项服务也包含持续性的现场支持以确保长期成果产出,并针对关键任务的上线,提供4小时内现场回应的选择性服务。 Supermicro数据中心解决方案与服务可助力客户完成从Bare-Land阶段的建置,到气冷转型液冷散热的程序。此外,现场建置服务可大幅缩短数据中心项目的前置时间。我们的整合型、一站式解决方案能缩短启动上线时间,并打造更高质量的数据中心。 Supermicro致力与客户合作,简化并缩短建置与部署先进数据中心所需的时间,而液冷散热也将是许多数据中心的必需技术。Supermicro的完整数据中心级产品组合可透过单一供应商形式为客户提供服务,进而实现更快的启动上线时间,同时确保更高质量的部署。

Supermicro

SMCI . 2025-10-17 1410

应用 | OPPO Find X9 Pro压感交互再升级 芯海科技赋能旗舰影像新体验!

10月16日,“OPPO Find X9系列暨智能生态旗舰新品发布会”隆重开幕。全球首发搭载ColorOS 16系统的Find X9系列旗舰手机,带来了流畅性与AI能力的全面革新。 作为OPPO Find系列的最新力作,Find X9 Pro在延续前代压感“抓拍快启键”交互设计的基础上,进一步优化了人机交互体验,为安卓旗舰手机的交互体验提供了更多可能。 影像系统是Find X9 Pro最引人注目的亮点。这款手机搭载天玑9500旗舰平台,配合与哈苏联合打造的专业影像系统,配备了哈苏全焦段超清四摄:包括5000万像素超动态大底主摄、2亿像素哈苏超清长焦镜头、5000万像素大光圈超广角镜头以及丹霞色彩还原镜头,实现了移动摄影的突破性提升。 该影像系统支持全焦段8K超清照片和4K 120fps杜比视界视频录制,从硬件层面奠定了专业影像的基础。其中,2亿像素哈苏超清长焦镜头表现尤为出色,支持3倍光学变焦、10cm长焦微距,更可通过外接哈苏专业增距镜扩展至230mm等效焦距,实现10倍无损光学画质,打造了“口袋中的完全体哈苏”。 压感技术在Find X9 Pro的影像创作场景中同样发挥了重要作用,抓拍快启功能让用户无需解锁屏幕即可快速进入拍摄状态,并提供更丰富的滑动及握持体验,确保用户不错过任何转瞬即逝的精彩瞬间。 从Find X8系列到Find X9 Pro,OPPO旗舰系列智能手机的压感交互技术持续进步。其操作体验更成熟,响应速度与准确度得到优化;功能应用更简洁,通过不同按压力度即可实现多种操作,简化了复杂功能的调用流程。 芯海科技压力触控系列方案集成了高精度测量AFE和电容检测模块的MCU,可轻松识别1g压力、0.1㎜滑动距离,具有功耗低、集成度高、体积小以及成本低的特点,为终端厂商提供了更具竞争力的解决方案。 未来智能手机的竞争,将不只是规格参数的比拼,而是用户体验的重构。自2016年率先开始进行压力触控芯片研发以来,芯海科技作为全球压感技术的引领者,压力触控系列产品历经四代的迭代创新,已广泛应用于智能手机、耳机通信、手表手环、智能家居、笔记本电脑、汽车电子等领域,赢得了众多品牌客户的信赖与好评。

芯海科技

芯海科技 . 2025-10-17 4035

企业 | 美光将退出中国服务器芯片业务

路透社10月17日报道,两位知情人士称,美光科技计划停止向中国的数据中心供应服务器芯片,该业务尚未从中国2023年的禁令中恢复过来。 2023年,中国网络安全审查办公室依法对美光在华销售产品进行了网络安全审查。据网信中国微信公众号2023年5月21日晚间发布消息,美光公司在华销售的产品未通过网络安全审查。按照《网络安全法》等法律法规,我国内关键信息基础设施的运营者应停止采购美光公司产品。 审查发现,美光产品存在较严重网络安全问题隐患。为此,网络安全审查办公室依法作出不予通过网络安全审查的结论。按照网络安全法等法律法规,中国国内关键信息基础设施的运营者应停止采购美光产品。 知情人士称,美光将继续向两家在中国境外拥有大规模数据中心业务的中国客户供货,其中包含笔记本电脑制造商联想集团。美光还将继续向中国汽车与手机行业的客户销售芯片。上一财年,美光来自中国大陆的营收为34亿美元,占总营收的12%。 当被问及退出中国数据中心业务时,美光在发给路透社的声明中表示,该部门已受到禁令影响,公司遵守经营所在地的适用法规。

美光

芯查查资讯 . 2025-10-17 3525

企业 | Nexperia芯片库存预计仅能维持几周

在美国威胁、中国对荷兰供应商Nexperia(安世半导体)实施出口管制后,可能引发连锁反应,导致生产线停产,汽车制造商正准备应对新一轮芯片供应中断。 据知情人士透露,欧洲制造商正在召开紧急会议,以应对可能在一个月内发生的供应中断。 在疫情引发此前芯片短缺后,汽车行业已增加库存。但知情人士表示,大众汽车等汽车制造商以及包括博世公司在内的供应商可能需要数月时间才能从受影响的荷兰制造商Nexperia转向其他供应商。 “如果紧张局势不能迅速得到解决,全球大部分汽车生产以及其他众多工业领域都可能陷入停滞,”德国电气和数字行业协会ZVEI主席Wolfgang Weber表示。 10月早些时候,中国商务部禁止Nexperia从其中国工厂出口产品。此举是为了回应荷兰政府夺取了Nexperia的控制权。Nexperia由闻泰科技所有,后者于2024年底被列入美国实体清单。 虽然Nexperia的芯片并非尖端技术,但它们应用广泛,构成了汽车供应链的关键环节,一辆汽车上就包含数百块芯片。其半导体用于控制开关或方向盘等功能。Nexperia 2024年营收为20.6亿美元,其中汽车行业贡献了60%以上的收入。 出口限制已经促使企业将目光转向其他领域。据知情人士透露,作为汽车行业主要供应商之一的德国芯片制造商英飞凌科技正在接到Nexperia客户寻求替代供应的电话。 汽车制造商不一定直接采购芯片,而是从博世、大陆集团和Aumovio等大型供应商那里购买包含半导体的成品零部件。这些公司还会从规模较小的供应商那里采购单个零部件,这使得快速评估潜在供应链中断的范围变得困难。 一封信函显示,Nexperia已告知其客户和业务合作伙伴,中国的出口管制构成不可抗力事件,将使该公司免于履行具有法律约束力的合同条款。该公司10月14日表示,正在与中国有关部门接洽,以获得出口限制豁免。除此之外,该公司拒绝发表评论。 大众汽车集团已成立一个工作组,调查其最大的供应商及其数百种零部件可能受到的影响。虽然大众汽车集团不直接采购Nexperia的芯片,但其中一些芯片被用于其汽车零部件。 该公司表示:“我们的生产目前未受影响。”并补充说,公司正在努力“及早发现潜在风险并决定必要的措施”。 博世表示,正在与其电子产品供应商之一的Nexperia进行接触。博世公司补充道,正在努力将任何潜在影响降至最低。 Nexperia在中国广东省设有组装工厂。据其网站显示,该公司还在德国和英国设有工厂,并在马来西亚和菲律宾设有两个组装中心。该公司拥有超过12500名员工,每秒生产约3000片半导体。 据欧洲汽车制造商协会称,业内目前的Nexperia芯片库存通常预计仅能维持几周,如果库存耗尽,生产可能会暂停。 “我们突然发现自己陷入了这种令人担忧的境地,”欧洲汽车制造商协会总干事Sigrid de Vries表示。“我们确实需要所有相关国家/地区迅速拿出切实可行的解决方案。”

安世

芯查查资讯 . 2025-10-17 1 7210

企业 | 英伟达 × ST联手突破!12kW/800V AI数据中心电源被塞进手机大小的配电板

近期,英伟达(NVIDIA)已完成对意法半导体(ST)12kW配电概念验证板的设计验证测试,这一成果标志着该项目正式迈入生产验证测试阶段。在开放计算项目(OCP)2025峰会上,这家GPU制造商展示了由意法半导体设计的完整12kW电力传输板样机。同时,ST也即将发布一份关于下一代人工智能数据中心高功率密度配电解决方案的白皮书,帮助工程师深入了解该电力传输板的工作原理,以及高功率密度的实现方式等。该白皮书将涵盖拓扑结构、设计考量、宽禁带晶体管、架构优化等核心内容。 意法半导体是英伟达新推出的800V机架配电开发计划中的重要合作伙伴。双方合作的核心原因是意法半导体研发的高功率密度电力传输板(PBD)。这款传输板采用小型化设计,却能承载12kW的功率。依托碳化硅(SiC)与氮化镓(GaN)功率芯片技术的最新突破、STGAP硅基嵌入式电隔离专利,以及先进的模拟数字信号处理能力,意法半导体正推动数据中心行业迈入新时代。借助这款电力传输板,英伟达得以缩减线缆体积、提升系统效率。此次合作实现了数据中心领域的一项重要突破:ST首次达成12kW电能持续输出,且能效超过98%;在输出电压为50V时,功率密度更是突破2600W/in³。 英伟达为何选择800V架构? 打破传统非可持续模式 过去数十年间,数据中心普遍采用48V配电系统,15kW功率的机架足以满足处理器、内存与外存的用电需求。但随着人工智能技术兴起与GPU应用市场爆发,这类场景需依托大型架构才能充分发挥并行运算优势,如今系统架构工程师面临着600kW至1MW大功率机架的设计挑战。电能需求的激增,迫使行业寻求全新电源架构——以48V电压输出600kW功率为例,需承载高达12500A的电流。仅需试想处理该功率所需的电缆、母线与散热器尺寸,便足以让不少工程师却步。 展望配电技术未来:800V成人工智能数据中心必备技术 要降低大功率输出所需的电流,最直接的方案便是提高输入电压。电流降低不仅能大幅缩减电缆与母线尺寸,还可减少交流电网与机架直流配电之间的电力变换环节。事实上,英伟达曾提及,相较于当前的54V配电系统,升级至800V平台可将能效提升最高5%。简言之,在超大规模数据中心可持续性备受关注的当下,升级至800V架构是提升资源利用率、从技术层面满足人工智能创新需求的最佳方法之一。 ▲ 800V是人工智能数据中心的必备技术 然而,设计理想配电系统仍面临挑战:需将800V高压转换为母线中压,进而生成GPU核心电压,同时要保证紧凑尺寸以适配服务器机架安装。机架的标准尺寸对配电系统的体积限制极为严格,而元器件的紧密排布又会加剧电磁干扰与热管理难题。因此,工程师需找到既能应对更高电压,又能保持紧凑外形的解决方案。此外,800V平台还需全新的电隔离与接地系统,安全保护机制及故障处理的复杂性也随之大幅提升。基于此,英伟达向意法半导体寻求技术支持。 ST如何实现紧凑空间内的12kW功率集成,达成2600W/in³功率密度? 满足带电插拔要求 为应对800V机架的固有挑战,同时满足计算机系统的带电插拔要求,意法半导体将解决方案分为两部分:带电插拔保护电路与电能功率转换器。其中,带电插拔保护电路采用意法半导体的1200V碳化硅(SiC)器件与电隔离型BCD(BIPOLAR-CMOS-DMOS)控制器。2021年,IEEE正式认可意法半导体为BCD系列硅半导体制造工艺的发明者。该工艺可整合模拟与数字元件,有效提升电源管理解决方案的效率与可靠性。与此同时,意法半导体在碳化硅器件领域拥有近30年研发经验,是首家将该技术应用于电动汽车的厂商。长期的技术积累,为我们应对此次挑战奠定了坚实基础。 ▲ STGAP产品 优化原边设计 解决方案的第二部分是DC-DC转换器,其功能是将整个机架的800V电压转换为单台服务器所需的50V电压。为在极小的机位空间内实现这一转换,意法半导体在原边采用650V氮化镓(GaN)晶体管堆叠式半桥架构,搭配STGAP电隔离栅极驱动器。得益于3.4eV的宽带隙和1,700cm²/Vs的电子迁移率使GaN具有独特的特性,可以实现低输出电容和较低的导通电阻,使其成为处理高频应用的理想材料。 优化副边设计 在副边设计中,意法半导体采用100V低压氮化镓(GaN)晶体管、低压栅极驱动器及STM32G4微控制器。这款微控制器的定时器分辨率低于200皮秒,能够实现与转换所需开关频率相匹配的高性能控制。同时,STGAP器件的优异隔离能力可实现电源转换器初级侧与次级侧的完全隔离,有效抵御电磁干扰(EMI)及其他可能影响紧凑型设计的异常情况。 变压器拆分设计:两组四单元架构 除精选元器件外,意法半导体还需应对严苛的空间限制,这意味着要缩减磁性元器件尺寸——尤其是10kV隔离设计已占用变压器的部分预留空间。为减少变压器磁芯用量,ST将传统大尺寸全桥拓扑拆分为两组架构,每组包含四个小型并联整流全桥。这种拆分设计可降低进入磁芯的磁通量,分散耗散功率;同时,采用四个小型全桥后,可使用更小的铁氧体磁芯,从而大幅缩减变压器整体尺寸。 上述元器件与拓扑解决方案,凝聚了意法半导体多年的技术积累与经验沉淀,正是这些专业能力让我们的方案具备独特优势。许多厂商需从外部采购相关元器件,而意法半导体可提供自研整体解决方案,这对配电系统优化至关重要。此外,新的800V配电架构也凸显了封装小型化、寄生电感最小化与双面散热技术的重要性——若器件尺寸过大或封装未经优化,根本无法实现如此紧凑的设计。而意法半导体始终致力于提供最小封装器件,这也是我们成为英伟达重要合作伙伴的关键原因之一。 全局视角:适配多元需求,推动行业升级 当前,业界正积极探索更高效的超大规模人工智能基础设施开发路径,不同企业选择了差异化技术方向。例如,部分企业正研发±400V系统。依托自身专业技术与产品组合,意法半导体可轻松复用现有电源转换设计方案,满足不同功率需求。事实上,我们可为所有寻求提升人工智能数据中心能效与可持续性的企业提供支持。 英伟达发布的测试公告及双方的合作成果具有重要意义和深远影响。目前,英伟达已批准ST的概念验证板,下一步将推进电路板制造与测试工作。这一里程碑充分体现了合作对数据中心格局的变革作用,实现了数年前难以想象的能效提升。英伟达的800V高压直流架构与意法半导体的配电板,共同标志着数据中心行业迈入新时代。

ST

意法半导体中国 . 2025-10-17 1410

技术 | 法规驱动,安全升维!IRED掀起座舱感知革命

感光百科:法规驱动,安全升维!IRED掀起座舱感知革命 当汽车从代步工具演变为移动的智能空间,一场关于舱内安全的静默革命正在上演。曾经的驾驶员监控(DMS)仅是防疲劳的“哨兵”。而今,在EURO NCAP、欧洲强制法规GSR等全球法规的强力驱动下,舱内传感正与DMS、乘客状态监控(OMS)等融合,进化为一个能感知舱内每一位乘员状态、并能与安全带、安全气囊等安全系统联动决策的“智能生命体”。 这场从“监控”到 “主动保护”的深刻变迁,不仅重新定义了汽车安全的标准,更对核心的传感光源——红外LED(IRED)提出了前所未有的性能与进阶需求。 舱内感知的“军备竞赛”,IRED成硬通货 当前,汽车舱内传感系统正经历着从基础到全面、从二维到三维的跨越式发展。其核心驱动力,源于全球法规体系对主动安全的日益严苛要求。以欧盟EURO NCAP为例,其评级标准从2023年仅占2分的DMS,急剧扩展到2026年涵盖儿童在场检测、驾驶员状态分析、突发疾病预警等全方位监控的25分体系。 这不仅是分值的提升,更是对舱内安全保护范畴的极大扩展,从单一的驾驶员注意力监控,延伸到对全舱乘员、各种体型坐姿乃至生命状态的精准感知。与此同时,中国的C-NCAP预计将紧随这一加严趋势,而更具强制性的国家法规也呼之欲出,旨在将舱内感知从“加分项”转变为新车上市的“准入门槛”。 这一趋势直接推动了技术方案的演进:能够提供深度信息、实现更精准人员定位与姿态识别的2D+3D融合传感,正成为迈向L3及以上高级别自动驾驶的必然选择。但当前由于技术指标、成本等多重因素,舱内3D传感的发展仍较为缓慢。 在此背景下,作为传感系统“眼睛”的IRED,其角色已从简单的补光灯,升级为需要提供更高功率、更均匀光照、更低热阻、更低电压等的发射器。整个行业对高性能、高可靠性IRED的强需求,因此被推至前所未有的高度。 IR:6芯片平台与光电效率飞跃 在应对舱内传感系统进阶对红外光源提出的“更高光效、更高辐照度、更低热阻、更低红曝、更小体积、更长寿命、均匀度更好”等核心提升需求,艾迈斯欧司朗推出了革命性的IR:6芯片技术平台,实现了IRED性能的阶跃式提升。 超过25%的亮度提升 IR:6芯片技术蕴藏了两项提升光效的“黑科技”。其一,芯片表面进行了特殊光学处理,大幅提升了整个表面的出光效率;其次,底层反射镜的反射能力显著增强,将更多原本耗散的光子有效反射输出。这两大技术协同作用,共同实现了在实验室环境下超过25%的亮度提升,为系统带来更高的光输出。 光电转换效率的行业标杆 IR:6通过焊盘位置、走线布局等芯片设计,显著提升了光电转换效率,其在25℃、1A驱动下达到61%,而且能在全温度范围内保持高位稳定(如在120℃高温下仍可达约50%),远超业界普遍30%多的水平。 高脉冲电流驱动能力,满足未来法规需求 此外,IR:6芯片平台还赋予了IRED更高的电流驱动能力。例如,在125℃、1ms、10%占空比条件下,最大允许脉冲电流从前代产品的1.5A提升至3.7A(基于IR:6芯片技术)。简单来说,如下图所示,将容许脉冲驱动电流的提升从图中的虚线提升到实线。 这直接满足了未来法规(如EURO NCAP)为提升探测精度、抗环境光干扰所要求的高电流、短脉冲驱动趋势,可以满足对包括穿透墨镜去捕捉驾驶员/乘客状态等细节高标准要求,为下一代DMS/OMS模组设计提供了关键性能储备。 系统级优化:热管理、光型设计与低红曝创新 除了芯片级的根本性突破,艾迈斯欧司朗在系统应用层面进行了深度优化,确保IRED性能在终端模组中得以高效、可靠地发挥。 热阻减半,系统实测:不只降温,更是性能与体验的双赢 在车载传感系统中,“热”从来不只是技术问题,更是用户体验与系统可靠性的核心挑战。当主机厂抱怨“模组烫手”、工程师为散热设计绞尽脑汁时,艾迈斯欧司朗的IR:6芯片技术,却从物理底层给出了一种“降温”可能。 基于IR:6芯片技术的新一代IRED产品SFH 472XXBS A01为例,其热阻显著降低至4.7K/W,市面主流水平约为7K/W,如下图曲线图所示。更低的结温意味着LED在高温环境下的光衰更小,寿命更长,为舱内传感系统在严苛工况下的长期稳定运行提供了保障。 在一项极具说服力的实测中,某主机厂仅将模组(包含DMS和OMS)中的LED更换为基于IR:6芯片技术的产品,未对系统做任何其他调整,结果令人惊喜,整体来看: 中心辐照度提升10.9%~13.4%——画面更清晰; 玻璃面罩温度降低~4℃——用户触摸不再烫手; PCB温度同步下降——系统寿命与稳定性显著增强。 这意味着,IR:6红外芯片技术实现了“既要亮度,也要凉度”的系统级突破。 精准光型设计:矩形光斑与倾斜角度照明,保证能量高效利用 针对OMS大视角应用场景,艾迈斯欧司朗主力推荐矩形光斑产品(如150°×135°、130°×110°),相较于传统圆形光斑,它能将光能更精准地投射到需要监测的区域,避免了边缘区域的能量浪费,显著提升了照明均匀度与系统能效。 而对倾斜角度的照明,也是考虑到能源的有效利用,放置顶棚过渡曝光。此外,通过倾斜角度照明的应用,可以达成组合提升均匀度的应用场景。 低红曝芯片技术:如何让舱内传感实现“隐形”守护 当夜幕降临,你是否曾在车内瞥见那些若隐若现的红色光点?这些被称为“红曝”的现象,正是车载传感系统与用户体验之间最直接的矛盾。为解决国内市场对“无感监控”的强烈需求,艾迈斯欧司朗开发了基于IR:6芯片技术的独特低红曝IRED产品。 在红外照明领域,工程师们一直在走“平衡之路”:波长越短(如850nm),人眼越容易看到红色光点;波长越长(如940nm),虽然“隐形”效果更好,但摄像头的灵敏度却会大幅下降。这个两难选择,让很多方案不得不做出妥协。 当大多数方案还在考虑给芯片或者镜头外加滤光片时,艾迈斯欧司朗选择了一条更根本的路径——让芯片自己学会“过滤”,通过在IR:6芯片内部植入特殊的吸收层,通过改变芯片自身结构,主动抑制人眼敏感的短波红外光(~850nm波段)。 此方案在不改变封装、不增加额外滤光片的前提下,实现了高效能低红暴,是成本与性能最优的综合解决方案。 *此图即为实现低红曝,基于IR:6芯片技术C版本方案集合 技术布局的终局思考:三阶IRED战略布局 在舱内传感的竞技场上,艾迈斯欧司朗用一套清晰的三阶产品战略,展现了其对技术演进与市场需求的深度洞察。 A版本:稳定基石 SFH 471x AS A01(850nm)与SFH 472x AS A01(940nm)构成了产品矩阵的坚实基础,满足当前市场对可靠性与成本效益的核心需求。 B版本:效能革命 基于IR:6芯片的B版本SFH 472x BS A01(940nm),实现了光电效率的跨越式提升 - 这不仅是一次参数进步,更是重新定义了红外LED的性能边界。 C版本:体验升华 此外,在B版本基础上,C版本融入了创新的芯片级低红曝技术,将技术优势转化为真实的用户体验提升,让科技在无形中守护驾乘安全。 这三级跳式的产品布局,展现的不仅是技术储备的厚度,更是对产业发展的前瞻思考。从满足基本需求,到追求极致性能,再到关注人性化体验,如何用扎实的产品路线图,为舱内传感的下一阶段发展指明方向,是产业链上游每个玩家都需要始终思考的核心。

艾迈斯欧司朗

感光现象 . 2025-10-17 2465

- 1

- 3

- 4

- 5

- 6

- 7

- 500