随着 AMD Spartan UltraScale+ 系列现已投入量产,解锁其功能集的最快途径便是采用最新 AMD Vivado 工具版本( 2025.1 或更高版本)和全新操作指南资源。该集成型设计套件能通过一键式时序收敛,将设计从 RTL 阶段推进到硬件阶段,从而帮助缩短迭代周期。让我们来看看该设计套件提供的功能特性。

统一流程,减少迭代次数

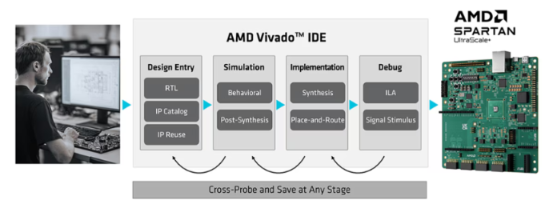

Vivado 工具流程将仿真、综合、实现、时序分析和调试整合到单个工具链中——并集成了流程的每个阶段:

通过多种途径的设计输入:RTL 导入、通过 IP Integrator 进行基于块的设计,或使用 AMD Vitis 统一软件平台导入使用 C/C++ 或 MathWorks® 开发的 IP。

仿真:使用 XSIM 在 RTL、综合后和布局布线后进行功能验证,以及硬件协同仿真。

综合与布局布线:内置的免许可综合功能与布局布线协同工作,助力实现 QoR 目标,包括引导流程和机器学习驱动算法,以快速满足时序收敛要求。

调试:使用 ChipScope 以系统内硬件速度采集和分析信号——直接在 Vivado 工具环境进行。

典型的设计循环可从 RTL 或基于 IP 的输入开始,通常使用 Vivado 工具中的 HDL 模板来创建计数器、状态机和其他常见结构,然后通过仿真进行验证。在实现之前,约束向导和 I/O 规划查看器可帮助确认时钟、I/O 布局和约束分组。设计检查点支持在任何阶段暂停和恢复综合或布局布线。随着 PCB 设计的演进,后期更改(例如 I/O 交换或引脚重新分配)可以通过增量编译高效处理。

快速迭代对于小型 FPGA 设计至关重要,每天进行多次迭代是常态,因此集成型流程避免了管理来自不同工具的中间文件的需求。面向 Spartan UltraScale+ 的 Vivado 设计套件教程视频演示了如何在一个项目中构建、仿真和实现完整的设计。

一键式时序收敛

要在一键式流程中满足时序要求而无需手动调整 RTL,这是 FPGA 设计人员面临的一个常见挑战。为了满足 FMAX(最大工作频率)目标而进行多次设计变更,一直是导致项目延误的常见原因。猜测哪些布局布线方案可能会改善 FMAX,然后等待数小时才能看到结果,并期盼获得更好的结果,这些过程可能会陷入“无休止”的循环。

Vivado 设计套件经过多个版本的调优,以满足最复杂 FPGA 和自适应 SoC 的 FMAX 目标。Vivado 设计套件 2025.1 版本和 Spartan UltraScale+ SU35P FPGA 结合使用时采用一键式流程,可在至高 250 MHz 的频率下实现平均 92% 的通过率1,无需任何设计变动,从而消除了为满足时序要求而反复试验的周期。设计人员可以依赖基于约束的流程、自动管道化和预优化的布局布线策略,无需深厚的工具专业知识或手动调优。

广泛、优化的 IP 产品组合助力快速开发

IP 复用是加速设计的关键,Vivado IP 编目提供了显著的领先优势——近 400 个预验证的软核,使您能够快速构建基础架构并专注于IP 差异化。Spartan UltraScale+ 高密度器件中新的硬块(包括 LPDDR4x/5 内存控制器和 PCIe® Gen4 )可助力进一步加速设计收敛,提供交钥匙性能。通过消除对可编程逻辑的需求,高端器件中的硬 IP 预计可将整体能效提升至多 60%2。

在 Vivado IP 目录中,您可以探索和实例化各种 IP——从基础组件到水平子系统(如 DSP、接口和内存控制器),一直到针对工业、汽车、视觉和其他市场的应用量身定制的垂直 IP。

利用 Vivado IP Integrator 这一通过 AXI 互连自动化简化组装的图形界面,能将硬 IP、软 IP 和自定义 RTL 相结合。

准备开始了吗

Spartan UltraScale+ 器件现已投入量产,AMD Vivado 设计套件的完全支持现已开放免费下载。无论您是 Vivado 工具新手、Spartan UltraScale+ 系列新手,还是两者兼而有之,专用资源页面都包含教程、视频、参考设计和文档,助您快速上手。

1. 基于 AMD 在 2025 年 7 月进行的最差负时序裕量测试,针对 AMD Vivado 设计套件 2025.1 版和 Spartan UltraScale+ SU35P FPGA,分别在 -1(最慢)速度等级(150MHz -250Mhz)下对 46 个设计,以及在 -2(最快)速度等级(200MHz – 250Mhz)下对 41 个设计进行了测试。结果因器件、设计、配置和其他因素而有所不同。 (VIV-018)

2. 预测基于 AMD 在 2024 年 1 月进行的内部分析,使用基于 AMD Artix UltraScale+ AU7P FPGA 逻辑规模计数的总功耗计算(静态功耗加动态功耗),借助 Xilinx 功耗估算器 (XPE) 工具 2023.1.2 版本,估算 AMD Spartan UltraScale+ SU200P FPGA 与 AMD Artix 7 7A200T FPGA 的总功耗对比。总功耗接口结果可能会在最终产品发布后,因配置、设计、使用和其他因素而有所不同。(SUS-006)

全部评论