SEI(Serial Encoder Interface)串行编码器接口,是先楫半导体创新性设计的一个针对串行绝对值编码器通信的外设。SEI支持同步通信模式与异步通信模式,既能做主机——从编码器获取数据,又能做从机——将位置信息以主机需要的串行协议发出。在电机类应用中大大的降低了编码器相关开发任务的难度,同时以硬件编解码的方式降低了CPU负载率,让CPU有更多算力处理其他任务。

先楫半导体SDK1.10.0提供了诸多SEI应用的实例,包括Biss-c、Endat、Hiperface、Nikon、SSI、Tamagawa等串行协议的主站、从站配置源码,开发者在sample实例的基础上,简单的进行修改即可应用到项目中。

本文以Biss-c和Endat协议为例,对SEI在同步通信中用法进行讲解,使读者对SEI的用法有进一步的认识与了解。

本文中,命令指协议中主站向从站发送的命令,从站需要根据命令内容进行回复或执行某些操作;指令指SEI引擎执行的动作。

1、SEI关键概念

1.1 数据寄存器

数据寄存器是SEI收发数据的数据存放单元。在通信的接收过程中,接收到的数据会被存放于数据寄存器中;在通信的发送过程中,需要向外发送的数据同样存放在数据寄存器中。

SEI共有17组数据寄存器,每个寄存器宽度为32bit。当SEI工作在同步模式时,数据线上连续出现的数据会根据clock信号进行采样,并将采样后的数据按照SEI配置依次保存到数据寄存器中,不超过32bit的圈数/位置数据可以使用1个数据寄存器进行保存,超过32bit的数据使用2个数据寄存器进行保存——不过单圈精度超过32位以及圈数超过32位的编码器比较少见,32bit寄存器可满足绝大部分使用场景。

数据寄存器0用于忽略接收到的数据——某些通信协议的数据字段,如果开发者不关心,可以使用数据数据寄存器0进行接收;其概念与Linux系统下黑洞文件类似。

数据寄存器2~数据寄存器17为通用数据寄存器。可以工作在3种模式下:

- 数据模式:仅用于存储数据。

- 检查模式:可设定期待值,例如用户期待接收到0x17,当接收到的写入该数据寄存器的值不为0x17时,可产生传输错误提示。

- CRC模式:用于收发数据过程中实时计算CRC值,可通过设置CRC多项式与CRC初始值来设计CRC算法,当接收数据的CRC计算结果与实时计算结果不符时,可产生错误传输提示。

1.2 命令寄存器

用于收发串行编码器协议中的命令数据。例如ENDAT协议中Mode Command字段为命令,其含义如下图:

可以看到,Mode Command字段内的M0~M3决定了通信的内容,根据该字段的不同,主机可以从编码器中读取位置数据、收发配置参数、复位等。

1.3 命令匹配表

命令寄存器接收到命令后,SEI引擎接收JUMP跳转指令,会根据命令内容在命令匹配表内进行检索。找到符合命令的表项后,则跳转至该命令匹配表指向的指令开始执行。SEI共支持8张命令匹配表,SEI引擎会以顺序方式对每张命令匹配表的命令进行对比,如果命令匹配表0~命令匹配表6都匹配失败,则无条件执行命令匹配表7的预设指令(回复/不回复)。命令匹配表一般在做从机时使用。

1.4 指令

SEI引擎共支持8种指令,分为停止、等待、接收、发送、跳转5大类指令,根据是否有超时保护拓展为8种指令。例如接收指令可分为时限内接收与无限时接收,时限内接收在规定的时间内未收到数据会进行报错处理,无限时接收则会永远等待下去。其它时限内发送与无限时发送等概念,请读者自行理解。

SEI共支持预设128条指令。

1.5 状态机

SEI状态机包括4个状态,状态的切换只能以0-->1-->2-->3-->0的顺序进行,每种状态的切换条件可由开发者自行定义,例如设置执行完第10条指令后状态机从状态0切换到状态1。状态切换可向外发送事件信号,开发者可将该信号拉到其它外设进行触发,实现硬件同步;或简单的产生一次中断或DMA事件,使用中断或DMA进行一定的数据处理工作。

理解SEI工作的关键就在于以上5个概念的掌握。其它更多的技术细节需要读者自行查阅UM手册进行理解。

2、BISSC指令表解析

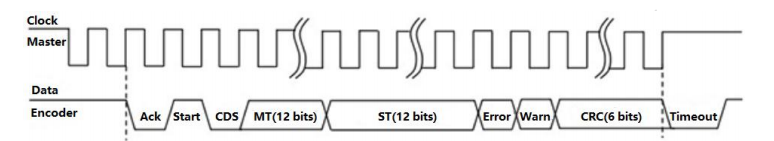

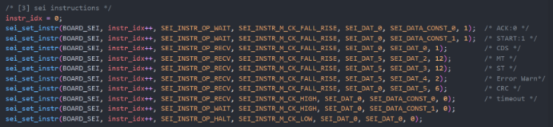

下面对SEI工作的流程进行直观的举例描述,时序如下图所示,代码参考samples\drivers\sei\master\bissc\src\sei.c:

1)主机SEI引擎使能后,对外发送clock信号,同时开始以指令0“等待”数据线上的ACK信号,ACK信号由编码器发出(编码器收到clock信号后会发出ACK表示应答),拉低数据总线电平,因此SEI收到ACK信号后会跳转到指令1;

2)按照协议,ACK响应后编码器发送1 bit高电平,代表开始数据传输,指令1“等待”数据线上的START信号,如SEI收到START信号,将继续接收CDS数据,跳转到指令2;

3)CDS和CDM是BISSC协议中用于主机与编码器进行一些控制指令交互的手段,主机每一帧数据传送1 bit CDM数据给编码器,编码器每帧数据传输1 bit CDS数据给主机完成交互。例程使用的编码器型号,不存在控制数据交互功能,因此1 bit的CDS数据没有意义,接收到数据后将其保存到数据寄存器0中,跳转到指令3;

4)主机SEI引擎接收12bit多圈数据保存在DATA_2中,跳转到指令4

5)主机SEI引擎接收12bit单圈数据保存在DATA_3中,跳转到指令5

6)WARN和ERROR是BISSC协议中用于表示编码器状态的数据bit,当故障时会通过这两个数据bit通知主机数据无效,例程使用DATA_4保存后,跳转到指令6

7)接下来6个bit的数据是用于数据完整性校验的CRC,CRC校验正确数据才有效,否则会触发SEI TRX中断,接收完6 bit CRC数据后会跳转到指令7

8)当数据发送完成后,Data 保持小于 10us 的低电平,这段时间被称为 Timeout。该信号一直维持到 Data 被拉高,表明当前帧通信结束,可以开始下一帧通信。在此期间,SEI主机不再向外发送clock信号,并维持CLK数据线为高电平。当编码器准备好下一帧数据传输,会释放数据线将其拉高为高电平,即指令8配置的等待数据线为1

9)完成整个通信过程后,主机执行HALT指令,准备下一帧数据的传输,重新从指令0开始数据传输

可以看到,通过以上工作流程的描述,SEI就依靠硬件自动完成了clock的发送,从编码器读回来了数据。CPU只要在数据寄存器中读取位置值和圈数值即可。

3、ENDAT指令表解析

与SEI类似,下面对ENDAT协议进行解析,时序如下图所示,代码参考samples\drivers\sei\master\endat\src\sei.c:

由以上时序图可以看到,ENDAT协议,由以下几个阶段组成:

1)由主机发送2个周期的clock信号

2)由主机发送Mode command(参见1.2章节),Mode command共6 bit,后3 bit与前3 bit按位取反

3)由主机再发送2个周期的clock信号

4)主机持续输出clock信号,开始等编码器给出start信号,start信号即编码器拉高数据线,

5)编码器传输1 bit Error数据

6)编码器传输n bit位置数据(n取决于编码器规格)

7)编码器传输5 bit CRC数据

8)一段时间的timeout,其概念与BISSC相似,区别在于编码器会拉低数据线表示timeout结束,即可以开始下一帧数据传输。

参照以上对ENDAT编码器协议的解读,理解下图所示例程的指令表设计,应该是毫无难度了。

4、同步通信其它技术点解析

4.1 采样点

细心的读者会注意到,SDK中BISSC与ENDAT两个master例程,采样点的设置不同,下面介绍一下采样点的设置。

BISSC例程如下,接收采样点为ck0 point,发送点为ck1 point:

ck0是指一个clock周期的第一个边沿,ck1是指一个clock周期的第二个边沿。结合BISSC协议的规定,idle状态下clock为高电平,那么第一个边沿就是下降沿,第二个边沿就是上升沿。

即意味着,SEI引擎会在下降沿采样接收信号线上的数据,在上升沿发送要发出的数据。BISSC协议主机不发送数据,只关注接收即可。

如下图为BISSC标准协议,可以看到,数据确实在clock的下降沿采样,上升沿数据发生变化。

ENDAT波形如下图,可以看到发送Mode command时,数据在下降沿发送;接收数据时,数据在下降沿采样:

所以ENDAT例程采样点配置如上图所示,clock信号线idle电平为高电平,那么接收采样点为ck0 point,发送点也为ck0 point。

4.2 采样点调整

当编码器线缆长度比较长,电信号的传输时间会对信号的相位发生影响,当影响无法忽略时,需要对采样点进行调整。

如下图ENDAT协议中所示,主机发出的clock在信号线上传输到达编码器,编码器根据clock信号发送位置数据,位置数据传输到主机时,如果主机仍然在下降沿采样,那么就会发生错误。

先楫SDK例程开发时充分考虑以上情况的发生,在SEI最初的通信过程中,会测量主机主动发出的clock信号下降沿与从机回复信号的start上升沿之间的时间差,来判断电信号在线缆中传输造成的相位偏移影响,对采样点进行调整,如下图代码:

调整的逻辑较简单,请读者自行分析,以便更好的理解整个通信过程。

5、小结

相信通过以上针对SEI的讲解,及对BISSC、ENDAT例程代码的分析,读者对SEI有了更深的认识,希望开发者可以用好SEI模块,加速项目开发与落地。

全部评论