2024年,Meta训练了一款AI模型“Llama 3”,并将相关训练成果汇总发表了一篇论文,受到广泛关注。在为期54天的预训练过程中,Llama 3遭遇了466次训练中断,其中意外中断高达419次。通过进一步调查,Meta了解到,这些异常中断中78%源自GPU及主机组件等硬件问题。

此类硬件问题不仅会导致工作任务中断,还可能导致静默数据损坏(SDC),造成意外数据丢失或异常,而这些问题往往长期难以被察觉。

Meta预训练时遭遇的中断虽出乎意料,但这种现象其实不难理解。像Llama 3这样的AI模型处理需求巨大,必须依赖超大规模计算集群支持。仅在训练环节,AI工作负载往往需要数十万个计算节点及其配套GPU持续协同工作数周甚至数月之久。

高强度、大规模的AI处理和数据交换会产生大量热量、电压波动和噪声,这些因素给计算硬件施加了巨大的压力。相较于以往的常规条件,GPU等底层芯片的退化速度大幅加快,性能和可靠性也随之下降。

这种情况在5nm以下制程中尤为突出,无论是制造环境和实际应用厂家,都能观察到明显的芯片退化和故障行为。

那么,我们该如何应对此类情况?又该如何减少意外中断和SDC?随着行业不断推出更新、规模更大AI工作任务,面对市场对处理能力与规模持续攀升的需求,芯片设计团队应如何确保最佳性能和可靠性?

确保芯片可靠性、可用性和可维护性(RAS)

以Meta为代表的AI创新企业已构建起完善的监控诊断体系,旨在持续改善计算环境的可用性与可靠性。然而随着算力需求激增、硬件故障频发以及SDC问题日益严峻,行业亟需建立更深层的测试与遥测能力,而且这种能力需要贯穿每个XPU/GPU内部的晶粒、多芯片封装以及互连架构等基础层面。

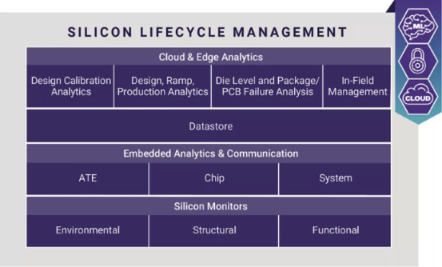

芯片生命周期管理(SLM)解决方案正是保障端到端RAS的关键所在,其覆盖范围贯穿芯片设计、制造、启动调试及现场运维全流程。

凭借更出色的可见性、监控和芯片层级诊断,设计团队可以:

通过遥测数据了解芯片故障或发生SDC的原因。

识别芯片组件、Multi-Die封装和高速互连中的电压或时序退化、过热和机械故障。

更精确地分析AI工作任务的热性能和功耗性能分析。

检测、特征分析和解决辐射、电压噪声以及可能引发位翻转和SDC的潜在故障机制。

提高芯片的良率、质量和现场RAS。

在寄存器传输级(RTL)设计阶段采用triple modular redundancy and dual core lock step(三模冗余和双核锁步等以可靠性为核心的技术),降低SDC风险。

建立准确的硅前老化仿真方法检测敏感或脆弱电路,并用抗老化电路替换。

优化可靠性模型中的异常检测(识别偏离正常行为的数据点),最大程度减少现场SDC。

新思科技SLM解决方案

作为系统设计的全球领导者,新思科技提供SLM IP和分析解决方案,可显著提升芯片健康状态,并在系统生命周期的各个阶段提供关键运行指标。

该解决方案具备三大监测特性,即环境监测、结构监测和功能监测,分别可以基于器件运行环境了解和优化芯片性能;识别从设计到现场运行阶段的性能变化;以及用于跟踪关键器件功能的健康状况和异常情况。

我们的SLM IP和分析解决方案包括:

工艺、电压和温度监测器

确保最优运行状态,同时最大化性能、功耗与可靠性。

全芯片高精度分布式监测,支持通过频率调节实现热管理。

支持28nm至3nm工艺节点。

路径裕量监测器

测量1000多条综合和功能路径(测试和现场)的时序裕量。

基于实际裕量优化芯片性能。

自动化路径选择、IP插入和扫描生成功能。

时钟和延迟监测器

测量一个或多个信号的边缘之间的延迟。

监测时钟占空比的质量。

借助内置自测(BIST)跟踪,测量内存读取访问时间。

对数字延迟线进行特征分析。

UCIe监测、测试和修复

监测Die-to-Die UCIe通道的信号完整性。

生成算法BIST向量,以检测互连故障类型,包括通道间串扰。

通过冗余分配执行累积通道修复(制造和现场)。

高速访问和测试

支持通过功能接口(PCIe、USB、SPI等)进行测试。

适用于现场运行以及晶圆分拣、最终测试和系统级测试。

可以与自动化测试设备结合使用。

通过减少引脚数量,方便现场远程诊断,降低测试成本。

高带宽内存(HBM)外部测试和修复

全面且经过硅验证的DRAM堆叠测试、修复和诊断引擎。

支持第三方HBM DRAM堆叠提供商解决方案。

高性能Die-to-Die互连测试和修复支持。

与HBM PHY协同工作,并支持一系列HBM协议和配置。

SLM分层子系统

面向片上系统(SoC)的自动化分层SLM和测试可管理性解决方案。

借助系统内调度,自动集成和访问所有IP/核心。

预先验证、随时可用的ATE向量和向量移植功能。

AI时代的芯片测试和遥测

随着AI器件和工作任务的规模和处理需求持续上升,系统可靠性、芯片健康和SDC问题愈发常见。虽然不存在能够彻底规避这些问题的单一解决方案或万能方法,但在芯片层级进行更深入、更全面的测试、修复和遥测,能极大缓解相关风险。其中,检测或预测现场芯片退化的能力尤为关键,这使我们能够在突发或灾难性系统故障发生之前及时采取纠正措施。

在AI技术快速演进的时代背景下,我们必须提供端到端的可见性和RAS保障,这使得芯片测试、修复和遥测的重要性与日俱增。

全部评论