重点内容速览:

1. Scale-up技术路线有哪些?

2. NVIDIA的NVLink技术

3. 亚马逊的NeuronLink方案

4. 华为的UB技术

5. 开放标准UALink技术

6. 通用PCIe技术

随着AI技术的飞速发展,AI服务器已经成为了支撑大规模模型训练和推理的核心基础设施。AI服务器的性能不仅依赖单个GPU的计算能力,更取决于多GPU之间的高效互连。纵向扩展(Scale-up)技术就是通过将多个GPU在单个机柜或节点内实现高速、低延迟互连,提升整体计算效能的关键技术。

超节点正成为各大厂商追逐的新方向,据市场预测,2025年全球AI超节点部署数量将达到数千个,其中北美约1900个,中国约1070个。也就是说,Scale-up正在从“可选”走向“必选”。本文将会重点介绍AI服务器Scale-up技术路线、市场格局,以及国内厂商的机会。

Scale-up技术路线有哪些?

所谓的Scale-up就是通过提升单台服务器的计算密度来扩展算力,例如可以在单台服务器中集成更多的GPU、更大的内存,更多的CPU,打造一个超节点,就像NVIDIA推出的NVL72机柜内就集成了72块高性能GPU。

也就是说,Scale-up通过在单一系统内增加GPU数量,并提供高带宽、低延迟的一致性互连,能够让所有GPU在同一地址空间内直接访问全部模型参数,避免跨节点网络通信的高延迟和带宽瓶颈,从而提升训练与推理的效率。

目前,各大厂商都在推出自研或深度定制的交换芯片与互联协议,比如专有协议NVIDIA的NVLink/NVSwitch、华为的UBSwitch、谷歌的ICI、亚马逊的NeuronLink、海光信息的HSL等;也有开放标准UALink、UEC/ULN;以及通用互连协议PCIe等。

市场占有率最大的非NVIDIA的NVLink和NVSwitch莫属,但随着UALink标准的正式推出,相关产品也开始陆续面市,渗透率开始逐渐提升,而且以太网技术也在不断发展,开始推出高带宽、低延迟的产品来抢占Scale-up市场份额。

连接下来我们一起看看这些技术路线都有什么不同。

NVIDIA的NVLink技术

其实最开始NVIDIA是采用PCIe技术来实现芯片之间的互联,但随着AI需求的增长,PCIe技术的带宽越来越满足不了高性能计算与AI工作负载需求,因此,NVIDIA在2016年首次推出了NVLink,实现了更快的GPU间通信,并构建了统一的内存空间。

接着2018年推出了NVLink Switch(交换机)技术,实现了8个GPU的网络拓扑中每对GPU之间的300GB/s的all-to-all带宽,为多 GPU 计算时代的scale-up网络奠定了基础。随后,在第三代 NVLink交换机中引入了NVIDIA可扩展分层聚合与归约协议(SHARP)技术,进一步提升了性能,有效优化了带宽性能并降低了集合操作的延迟。

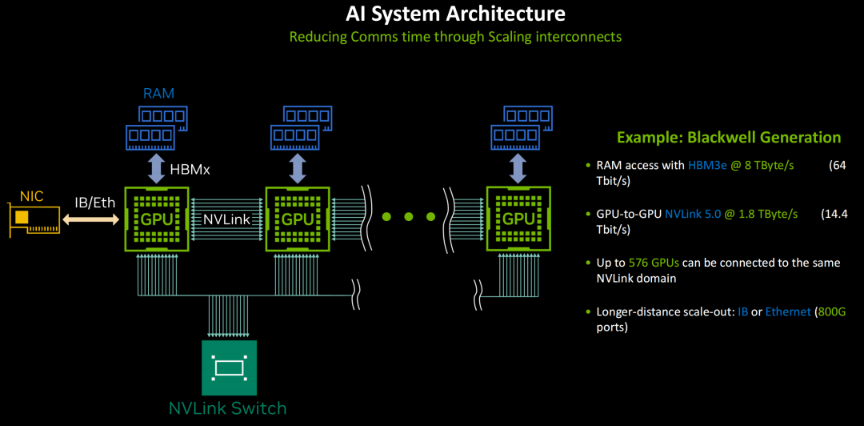

到了2024年,NVIDIA推出了其第五代NVLink技术,进一步增强的 NVLink交换机支持72个GPU实现全互联通信,通信速率双向达1,800 GB/s(18链路×100GB/s),聚合总带宽高达130 TB/s,较第一代产品提升了 800 倍。通过NVLink交换机在无阻塞计算架构中支持最多576颗GPU互连。NVLink连接的GPU被称为“POD”,具有独立的数据和计算域。

据NVIDIA的规划,他们将在2026年推出NVLink6技术,实现3,600GB/s的通信速率,576块GPU互联。2027年推出NVLink7,2028年推出NVLink8,进一步提升带宽、降低延迟,并优化互连拓扑的灵活性。

在2025年的Computex大会上,NVIDIA推出了NVLink Fusion,旨在像第三方CPU和加速器厂商开放NVLink生态系统,通过发布IP和硬件推动第三方设计与NVIDIA芯片实现互操作。该技术可让定制芯片(包括CPU与XPU)与NVIDIA的NVLink Scale-up网络技术及机架级扩展架构相集成,从而实现半定制化的AI基础设施部署。目前NVLink Fusion的合作伙伴包括AIchip、Astera Labs、Marvell、联发科技、富士通、高通、Cadence及Synopsys等厂商。

亚马逊的NeuronLink方案

亚马逊云科技的专有Scale-up技术是NeuronLink,该技术能将多台Trainium服务器组合成一个逻辑上的单一服务器,连接带宽可达2TB/s,延迟1us。通过NeuronLink连接后,芯片之间可以直接访问彼此的内存,就像是一台超级计算机一样工作。

比如其Trainium2 UltraServer就包含了64颗Trainium2加速器,可提供83.2万亿次每秒浮点运算能力,6TB HBM高速内存,以及185TB/s的HBM内存带宽。

其实NeuronLink协议的底层是基于PCIe协议实现的,例如 NeuronLink v3版本采用了PCIe 5.0作为其物理层协议,每个通道单向传输速率为32Gbit/s,通过多通道聚合实现高带宽通信。例如Trainium2 UltraServer使用AEC做柜间互联,DAC做柜内互联,单颗芯片基于 NeuronLink v3(对标NVLink)可实现640GB/s(双向1.28 TB/s)芯片间带宽,与服务器内6颗芯片实现互连,支持内存池化与大规模横向扩展,提升集群整体协同效率。

华为的UB技术

华为最近推出的CloudMatrix 384 AI算力集群系统,包含了16个机柜,其中12个是计算机柜,每个机柜部署了32颗昇腾910C芯片,其余4个机柜作为光互联核心,配备了6,912个400G光模块,实现了384颗昇腾910C芯片之间的全对全高速无阻塞互联,总算力达到了300PFLOPS。

这背后的Scale-up技术就是其超高速低延迟统一总线(UB)网络来实现计算、内存和网络资源的动态池化与统一访问的。

开放标准UALink技术

2024年5月,AMD、博通、Cisco、Google、HPE、Intel、Meta 和Microsoft达成一致,将制定一项新的行业标准,专用于推动数据中心用Scale-up AI系统连接的高速低延迟通信。该初始小组将定义并建立一个开放的行业标准,称为超加速器链路 (UALink)。这就是UALink联盟的由来。

2025年4月UALink联盟正式发布UALink 1.0,定义了一种高速、低延迟的加速器互联,支持每通道最大双向数据速率200GT/s,信号速率为212.5GT/s,以适应前向纠错和编码开销。UALink可以配置为x1、x2或x4,四通道链路在发送和接收方向上均可达到800GT/s。一个UALink系统支持多达1024个加速器(GPU或其他)通过UALink交换机连接,每个加速器分配一个端口和一个10位唯一标识符,用于精确路由。UALink电缆长度针对小于4米进行了优化,能够实现小于1微秒的往返延迟,支持64B/640B负载。这些链路支持跨1到4个机架的确定性性能。

目前还没有UALink的产品面市,但进展迅速。AMD、英特尔、Astera Labs、Marvell、Synospsys等厂商在产品落地方案都在积极推进。例如,AMD的AI一体机“Helios”采用的的UALoE(UALink over Ethernel)方案,就是在底层使用以太网物理层和交换芯片来承载UALink协议数据。可以利用现有的Ethernet交换机、布线和生态,但在链路层之上运行UALink定义的高性能互连协议。Helio UALoE 72包含18个均匀分布的计算托盘(顶部9个,底部9个),每组计算托盘中间配置6个UALoE交换托盘。每个计算托盘搭载4块 MI400 GPU,每个交换托盘则配备2个Tomahawk6 102.4T以太网交换机(每个通道200G速率)。

博通的SUE以太网技术

虽然2024年5月份的时候,博通有参与成立UALink联盟,但在2205年6月的报道中,博通的名字已经从UALink联盟官网中移除,且开始大力推广其Scale-up Ethernet(SUE)技术。该技术是博通在2025年4月都柏林开放计算项目(OCP)上宣布推出,旨在实现GPU与GPU之间的通信标准,其落地产品包括其今年6月份新推出的Tomahawk6系列芯片和7月份推出的Tomahawk Ultra芯片。

其中Tomahawk6系列在单个芯片中可实现102.4Tb/s的以太网交换,Scale-up集群规模最大为512个XPU,两层Scale-up网络中支持超过10,000个XPU相连,每个链路为200Gb/s,支持长距离无源铜缆连接,适用于任何NIC或XPU以太网终端节点。

Tomahawk Ultra针对高性能计算和AI集群的需求进行了针对性优化。在延迟与吞吐量方面,该芯片在51.2Tb/s的满负载下,可实现250ns的转发延迟,即使处理64字节的最小数据包,也能保持每秒770亿个的线速包交换能力。在SUE规范的配合下,可实现低于400ns的端到端通信延迟。这打破了传统以太网“高带宽与低延迟不可兼得”的局限。

效率优化上,Tomahawk Ultra采用了自适应以太网头部设计,将传统46字节的头部开销缩减至10字节,且完全符合以太网规范。这样调整后,显著提升了带宽利用率,尤其适用于AI场景中小数据包密集传输的需求。

可靠性方面,该芯片通过链路层重试(LLR)和基于信用的流量控制(CBFC)构建了无损传输架构。其中,LLR借助前向纠错机制检测并自动重传错误数据包,避免物理层丢包;CBFC则通过实时监控缓冲区状态,防止因溢出导致的数据包丢失,解决了以太网在高负载下的可靠性问题。

博通之所以推出SUE技术,应该有三个方面的考虑,一是技术复用与生态协同,利用UEC超级以太网中已经成熟的降低延迟功能,可以避免重复开发,同时借助UEC生态链的产业共识,降低与AI芯片厂商的对接障碍;二是市场主导与商业利益,SUE作为AI芯片互连的规范,需要依赖博通的芯片实现落地,这样既推动了标准化,又巩固了其市场地位;三是开放性优势,SUE是基于以太网技术的开放性标准,更容易被产业所接受,有助于扩大市场份额。

采用SUE技术,能够享受超低延迟的AI特性,从而为高性能计算提供更好的支持。

通用PCIe技术

PCIe,即PCI-Express,是一种高速串行计算机扩展总线标准,它原来的名称是“3GIO”,由英特尔在2001年提出,旨在替代旧的PCI、PCI-X和AGP总线标准。在PCIe交由PCI-SIG认证发布后正式改名为PCI-Express,简称PCIe。

2003年,PCI-SIG推出了PCIe 1.0a,每通道数据速率为250MB/s,传输速率为2.5GT(GigaTransfer)/s。传输速率表示为每秒传输量,不是每秒位数,因为传输量包括不提供额外吞吐量的开销位,例如PCIe 1.x使用的是8b/10b编码方式,导致占用了20%的原始信道带宽。

2007年,PCI-SIG提出PCIe 2.0规范,传输速率提升至5GT/s,每通道吞吐量提升至500MB/s。

2010年,推出PCIe 3.0,传输速率进一步提升至8GT/s,每通道吞吐量为984.6MB/s。PCIe3.0将编码方案从8b/10b升级到了128b/130b,将带宽开销从PCIe2.0的20%降低到了约1.54%。

2011年11月底,PCI-SIG初步公布了PCIe4.0,传输速率为16GT/s,每通道吞吐量为1.969GB/s。2017年6月8日正式发布最终版PCIe4.0规范。

随后PCIe标准多年都没有更新,直到2019年5月才发布PCIe5.0。2022年正式发布PCIe6.0标准。2025年推出7.0标准。

近年来,随着AI时代的到来,过去进展缓慢的PCIe标准,这几年发展迅速,到目前为止,已经完成了PCIe8.0草案的制定,且草案版本已到了PCIe8.0 v0.3版本。

虽然标准进展加快了,但落地的硬件产品目前主流仍为PCIe5.0,还有不少场合还在使用PCIe4.0产品。

在现有的计算架构中,CPU、GPU,以及SSD等芯片的I/O端口数量有限,一方面如果没有交换机芯片,端口数量会直接限制整体系统的互连带宽;另一方面,当前大多数的CPU仍然是基于x86架构,而PCIe标准是英特尔主导制定的,因此在CPU与GPU互连的场景中,几乎都需要使用PCIe交换机芯片。

可以提供PCIe交换机芯片的企业也有不少,比如博通的PEX系列、Astera Labs的Scorpio系列等;国内的数渡科技和中兴微等有相关产品,澜起科技在PCIe中继器(Retimer)上技术积累深厚,未来有望切入PCIe交换机芯片领域。

结语

未来随着AI时代的发展,推理端的需求将会超过训练端的需求,而小批量、低精度、MoE等推理任务对计算本身的要求不高,但在分布式部署下,多卡之间的通信延迟往往成为效率的瓶颈。因此,行业对机柜内部的Scale-up网络需求更多。

与之前AI训练市场份额更大时,NVIDIA的GPU加上其NVLink技术占据了市场绝对主流,但在推理市场,GPU的产品形态更加多样,除了NVIDIA的GPU,还有各个云厂商自己定制的推理芯片,还有国内华为、寒武纪、海光信息、昆仑芯、平头哥、燧原科技、摩尔线程等厂商不同的GPU产品或AI芯片,他们采用了不同的Scale-up技术。

也就是说,未来推理市场的芯片种类更加多样化,与之相应的Scale-up技术也将百花齐放,以太网、PCIe、UALink等开放标准,以及各自的专有技术将都有机会在市场中占有一席之地。

全部评论