OSPI Flash(Octal SPI Flash)是一种基于SPI(串行外设接口)扩展的高速串行Flash存储器,采用8-bit数据总线通信方式。相比传统的SPI或Quad SPI(QSPI),OSPI提供更高的数据吞吐率与更优的系统性能。OSPI Flash主要应用在高性能嵌入式系统启动,图形界面处理(GUI)/人机交互界面(HMI),嵌入式AI模型存储等领域。瑞萨高性能MCU、MPU都提供了功能强大的OSPI接口,它不仅可以工作在8线的高速模式下,还兼容普通的单线(SPI),双线(DSPI)和四线(QSPI)的多种工作模式和多种协议模式。

然而面对广大不同厂家的OSPI Flash,虽然说大部分功能相似,大部分功能也可以复用,但是不同厂家的OSPI Flash还是存在或多或少的差别。因此如果客户出于成本的考虑,需要更换OSPI Flash的时候,需要做驱动层的适配工作。那如何做OSPI Flash的驱动的适配工作?

下面我以Renesas RA8D1这款高性能MCU为例来说明如何进行OSPI Flash驱动的适配工作,总结成两篇适配秘籍,可以供客户参考。公欲善其事,必先懂其基(基本原理),本篇文章先就OSPI的一些工作模式和协议等基本概念做一个相对系统的介绍。后续的篇章我们将以Winbond W35T51NW OSPI Flash为例来展开具体的驱动的适配工作。请感兴趣的读者持续关注!

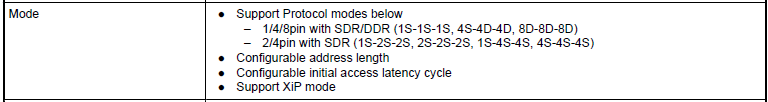

读者朋友们可以先了解一下RA8D1的OSPI specifications:

RA8D1的OSPI工作模式:

Support Protocol modes below

xSPI规范支持多种协议模式,包括1S-1S-1S、4S-4D-4D、8D-8D-8D、1S-2S-2S、2S-2S-2S、1S-4S-4S、4S-4S-4S等。这些模式主要是基于数据传输位宽(线数)和时钟模式(SDR/DDR)进行区分。

协议模式的基本概念

1S、2S、4S、4D、8D代表了数据传输过程中使用的线数:

○ 1S(Single Line,单线):每个时钟周期传输1bit数据。

○ 2S(Dual Line,双线):每个时钟周期传输2bit数据(双线,每根线1bit)。

○ 4S(Quad Line,四线):每个时钟周期传输4bit数据(四线,每根线1bit)。

○ 4D(Qcta Line,四线DDR):每个时钟周期传输8bit数据,因为采用DDR(DDR双数据速率)模式,时钟周期的上升沿传输4bit数据,下降沿传输4bit数据。

○ 8D(Octa Line,八线DDR):每个时钟周期传输16bit数据,因为采用DDR(DDR双数据速率)模式,时钟周期的上升沿传输8bit数据,下降沿传输8bit数据。

SDR(Single Data Rate,单数据速率)DDR(Double Data Rate,双数据速率):

○ SDR:仅在时钟上升沿传输数据。

○ DDR:在时钟上升沿和下降沿传输数据,线数相同的情况下吞吐量是SDR的2倍。

具体模式说明

不同模式的主要区别在于xSPI接口访问Flash的地址、命令和数据阶段分别使用多少条数据线进行传输。

| 模式 | 命令阶段 | 地址阶段 | 数据阶段 | 时钟模式 |

| 1S-1S-1S | 1-bit | 1-bit | 1-bit | SDR |

| 4S-4D-4D | 4-bit | DDR4-bit | DDR4-bit | DDR |

| 8D-8D-8D | DDR8-bit | DDR8-bit | DDR8-bit | DDR |

| 1S-2S-2S | 1-bit | 2-bit | 2-bit | SDR |

| 2S-2S-2S | 2-bit | 2-bit | 2-bit | SDR |

| 1S-4S-4S | 1-bit | 4-bit | 4-bit | SDR |

| 4S-4S-4S | 4-bit | 4-bit | 4-bit | SDR |

下面以1S-1S-1S、4S-4D-4D、8D-8D-8D三种协议模式举例说明

1S-1S-1S(传统SPI模式)

○ 命令、地址、数据阶段都使用单线传输(每个时钟周期1bit)。

○ 这种模式兼容传统SPI,但传输速度较慢。

○ 优点:兼容性好,适用于低速SPI设备。

4S-4D-4D(Quad SPI DDR模式)

○ 命令阶段:使用4-bit传输(相比1S提高4倍)。

○ 地址阶段:使用4-bitDDR传输(时钟上升沿和下降沿都发送数据)。

○ 数据阶段:使用4-bitDDR传输,吞吐量更高。

○ 优点:相比1S-1S-1S,吞吐量提高了8倍,适用于高速NORFlash存储应用。

8D-8D-8D(Octa SPI DDR模式)

○ 命令、地址、数据都使用8-bitDDR传输。

○ 相比4S-4D-4D,吞吐量翻倍。

○ 适用于极高速NORFlash存储,如PSRAM、Octa Flash、Octa HyperRAM。

Configurable address length

支持可配置的地址长度(常见如24-bit或32-bit地址模式):

24-bit通常用于小于16MB(128Mbit)的Flash;

32-bit用于更大容量的Flash(>16MB);

Configurable initial access latency cycle

指访问延迟周期(Latency Cycle)可配置,在XIP或连续读取模式中尤为关键:

设备允许设置dummy cycle数量;

适应不同主频、控制器时序要求;

优化带宽性能或兼容性。

Support XiP mode

支持Execute in Place(XIP)模式:

MCU/MPU可将Flash映射入内部地址空间;

支持直接读取并执行,不需复制到RAM;

通常与memory-mapped mode、持续读取命令组合使用。

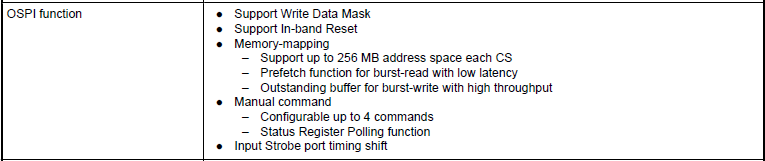

RA8D1的OSPI接口功能:

Support Write Data Mask(支持写数据掩码)

允许在写入数据时屏蔽某些字节,使其不被改写,而其他字节仍然可以被正常写入。

这种功能通常用于按位更新存储器内容,而无需先读取、修改、再写入完整数据。

Support In-band Reset(支持带内复位)

通过OSPI总线上的指令或数据序列触发设备复位,而不是依赖额外的硬件复位引脚。

○ 适用于系统集成度高、不易接触硬件复位引脚的应用,如嵌入式系统和工业控制设备。

Memory-mapping(内存映射模式)

OSPI控制器支持将外部Flash设备的存储空间直接映射到MCU地址空间,使其像内部RAM/ROM一样被访问。

Support up to 256MB address space each CS(每个CS支持高达256MB的地址空间)

在内存映射模式下,每个片选(CS,Chip Select)可支持高达256MB的存储空间,这意味着可以使用较大的外部存储器。

应用场景:

○ 适用于大容量代码存储(如执行XIP(execute In Place)),即代码直接在Flash中运行,而无需拷贝到RAM。

○ 适用于存储大量数据,如日志记录、固件存储、AI推理模型等。

Prefetch function for burst-read with

low latency(预取功能,提高突发读取性能)

在突发读取(BurstRead)模式下,OSPI控制器会提前读取后续数据并存入缓冲区,减少访问延迟。

应用场景:

○ 适用于实时性要求较高的应用,例如高速图像处理、实时操作系统(RTOS)等。

○ XIP模式下,可以减少CPU访问外部Flash的延迟,提高程序运行效率。

Outstanding buffer for burst-write with high throughput(突发写入优化,提高吞吐量)

突发写入(BurstWrite)时,OSPI控制器使用Outstanding buffer(写入缓冲区),允许CPU快速提交数据,而不必等待Flash完成写入,提高吞吐量。

应用场景:

○ 适用于数据流量较大的应用,如数据记录、固件升级、机器学习模型加载等。

Manual command(手动指令模式)

OSPI支持手动发送自定义指令,使其适用于不同厂商的Flash设备,并提供更灵活的操作方式。

- Configurable up to 4 commands(可配置最多4条指令):用户可以预设4条常用指令(如读、写、擦除等),减少软件控制开销,提高效率。

- Status Register Polling function(状态寄存器轮询功能):允许MCU轮询Flash的状态寄存器,以确定Flash是否完成写入、擦除等操作,避免不必要的等待。

Input Strobe port timing shift(输入同步信号端口的时序调整)

在高速OSPI传输中,数据可能会有时序偏移。这个功能允许调整数据采样时钟,以确保数据稳定可靠。

应用场景:

○ 当使用不同的Flash器件时,可能会因工艺或PCB布局导致时序误差,调整该参数可以优化信号完整性。

○ 适用于高速通信场景,如工业自动化、汽车电子、无线通信设备等。

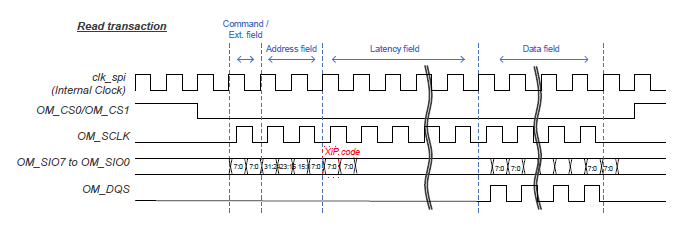

下面具体给读者解读一下在8D-8D-8D协议下的时序图:

点击查看大图

图中相关信号线的含义如下表所示:

| 信号 | 含义 | 说明 |

| clk_spi(Internal Clock) | 控制器内部工作时钟 | 控制器使用的内部时钟,驱动SPI状态机,不直接输出 |

| OM_CS0/CS1 | 片选信号 | 有效为低,表示与Flash通信开始 |

| OM_SCLK | 外部SPI时钟 | 控制器发出的时钟信号,Flash据此采样或发送数据 |

| OM_SIO[7:0] | Octal IO数据线 | 8位数据总线,双向通信(收发命令/地址/数据) |

| OM_DQS | 数据选通信号 | DDR模式下Flash输出的时钟对齐信号,用于控制器采样数据 |

从上图可以看到command field的一个时钟周期的上升沿可以采集8位数据(因为有OM_SIO0-OM_SIO7八根线的数据,每根线上一位数据),下降沿也可以采集8位数据,这样一个时钟周期可以采集16bit的数据。同样的道理地址段两个时钟周期,可以采集32位数据。那么这样数据段的传输速率,相比1S-1S-1S协议提高了16倍。

全部评论