存储器有内存(Memory)和存储(Storage)之分,前者为易失性存储器,比如DRAM;后者为非易失性存储器,比如NAND Flash。

存储器的历史始于1984年,彼时Masuoka教授发明了 NAND Flash(NAND闪存)。1989年,东芝首款NAND Flash上市。2001年,许多Flash厂商推出MLC NAND Flash。2007年,东芝推出3D NAND,三星也在2012年发布其第一代3D NAND。NAND Flash技术几十年发展保留了相同的概念、堆叠(stack)和架构,存储密度随时间呈指数增长。

2010年以后,嵌入式存储器(embedded memories,指“集成在片内与系统中各个逻辑、混合信号等IP共同组成单一芯片中的存储器”)开始达到28nm节点,但是,存储器单元(cell)在面积收缩能力、复杂度进展缓慢,技术迭代的压力被转移到新兴内存和更先进的工艺节点上。

2015年,英特尔和美光公司开发了基于相变存储器(PCM)的3D XPoint技术,填补DRAM和Flash之间的延迟差距,使新内存架构成为可能,也为非易失性内存(NVM)领域带来了创新。自2017年起,这项技术以Optane品牌在公开市场上市。峰回路转,2021年美光不再认为3D Xpoint的持续投资是合理的,宣布放弃3D Xpoint;2022年业界传出消息,英特尔正在关闭Optane业务部门。

3D XPoint未成气候,或许表明“方向比努力更重要”,新技术要有市场,关键在于能否解决应用的计算和内存瓶颈。例如,模拟人脑的计算系统往往要求高能量效率、并行性以及诸如对象识别、联想、适应和学习的认知能力,对计算和内存之间的协同工作提出新要求。

此外,社交网络、流媒体和视频点播等的消费电子应用,以及智能家居、智慧城市等物联网应用盛行,连接网络的智能设备大量增加,数据量和数据中心增长快速,计算系统的能量消耗更多地受到数据传输的影响,而不是计算本身。

面对上述问题,业界需要计算系统结构的新规范,导致了以内存为中心和“存内计算in-memory computing”系统的兴起。在进一步探讨这些技术之前,不得不提一下近期存储器的行情走向。

需求低迷、上游原厂减产,库存调整或贯穿2023年

存储器市场存在较强的周期性,交替出现短缺或者供应过剩的时期,导致价格变化、收入波动等情况,当前存储器市场有几个情况。

首先是降价。综合媒体和研究机构的消息,存储器的供需处于失衡状态。TrendForce集邦咨询报告显示,NAND Flash正处于供过于求的状态,下半年起,买方着重去化库存,大幅减少采购量,卖方开出破盘价以巩固订单,使第三季晶圆(Wafer)价格跌幅达30~35%。但各类NAND Flash终端产品仍疲弱,原厂库存因此急速上升,导致第四季NAND Flash价格跌幅扩大至15~20%。而绝大部分原厂的NAND Flash产品销售也将自今年底前正式步入亏损。原因是在高通胀影响下,消费电子产品需求疲软,第三季存储器出货量呈现每个季度递减的趋势,终端买方因存储器需求明显下滑而延缓采购,导致供应商库存压力进一步升高。

类似的,各DRAM供应商为求增加市占的策略不变,市场上已有“第三、四季合并议价”或“先谈量再议价”的情形,皆是导致第四季DRAM价格跌幅扩大至13~18%的原因。

其次是减产。部分供应商在运营陷入亏损的压力下,减产以降低亏损是可能的对应方式。芯查查APP显示,美光已经于9月底宣布削减DRAM和NAND Flash的产量,成为头家正式降低产能利用率的制造商,并强调其在2023年大幅下调资本支出,DRAM生产比特的年增长率仅为5%左右。

NAND Flash市场形势比DRAM更为严峻,主流产能晶圆的平均合同价格已经下降到现金成本,并且正在接近各个制造商亏损销售的边缘。Kioxia(铠侠)在美光之后相继宣布,将从10月份起将NAND Flash产能利用率降低30%。DRAM目前的合同价格仍然高于主流供应商的总生产成本,因此与NAND Flash相比,是否会有进一步的减产还有待观察。

减产对于芯片原厂的产品升级计划造成影响。美光原计划从四季度开始逐步提高232层NAND Flash的比例,减产之后,主流工艺估计2023年仍以176层产品为主。Kioxia和WDC原计划从四季度开始迁移到162层产品,但是WDC减少2023年资本支出,加上需求能见度低,无法实现原定计划。

图注:天使投资人、知名互联网专家郭涛

针对存储器近期行情,编辑部采访天使投资人、知名互联网专家郭涛,他表示,当前存储芯片领域已出现明显供过于求局面,库存持续高企,未来市场将经历漫长消化库存阶段,厂商减产暂时不会对供应链带来影响。随着存储芯片库存大幅增长,存储芯片价格也出现滑落,汽车、电脑、手机、存储服务器等行业获益。整体来看,明年存储芯片市场依旧是供大于求的局面,伴随着存储芯片企业的减产和去库存,在2024年第一季度有望实现供求平衡。

图注:洛克资本合伙人李音临

洛克资本合伙人李音临介绍道,三星、SK海力士、美光三巨头主导了DRAM市场,其中三星市占率为43%左右、SK海力士市占率27%左右,美光市占率24%左右。内存大厂降低了产能利用率反映对消费电子经济周期的悲观,也是对全球内存库存高企的悲观。消费电子的销量与全球居民收入以及对未来的前景预期紧密相关,在全球高通涨+国际大环境不稳定的形势下,居民对消费更为谨慎,打击了消费电子需求。

内存大厂面临宏观需求萎靡,还有微观层面库存的高企。2021年消费电子需求正旺的时期,大量全球的电子元器件经销商和下游集成商出于投资或提前囤货的动机,积累了大量的内存库存,原本预期2022年可顺利出货,但现实未能如愿,现在全球内存大厂即使降低了出货量,也要等待下游慢慢消化库存,而在经济衰退周期去化又雪上加霜。

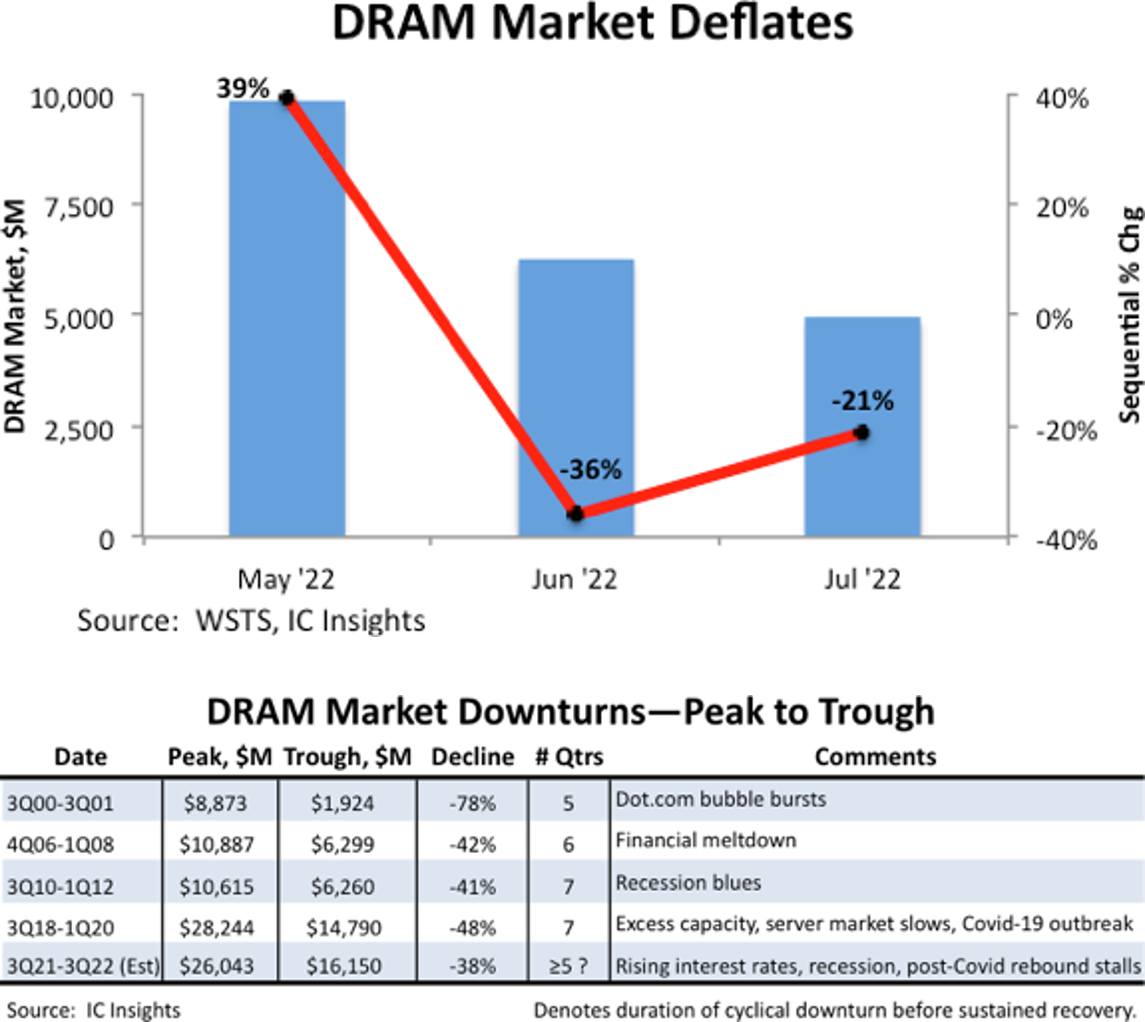

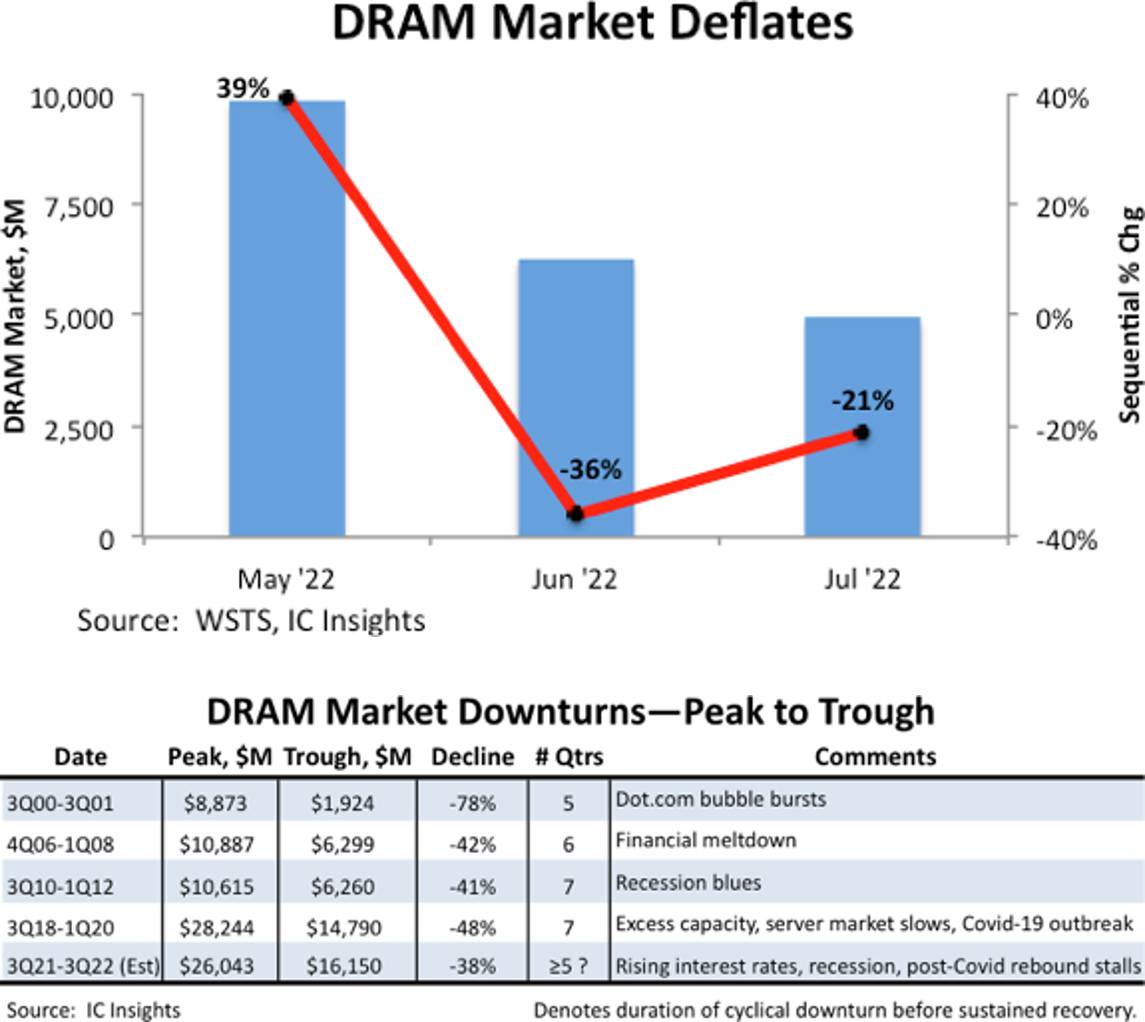

作为主要的内存芯片,DRAM在过去两年经历了上升周期,但是到了2022年情况有所改变。IC Insights数据显示,从2020年下半年开始持续到2022年5月的DRAM市场强劲回升已经结束。DRAM在5月份公布两年多来的最高月销量后,销售额在6月份下降了36%,7月份又下降了21%。市场崩溃是陡峭而迅速的,以至于7月份的DRAM市场规模约为5月份的一半。对飙升的通货膨胀和经济衰退的担忧,削减了消费者对新智能手机、电脑、电视和其他电子产品的支出;同时,系统制造商也缩减了新的DRAM订单,理由是需要消耗现有库存。自2000年以来,DRAM市场经历过几次衰退,每次衰退至少持续5个季度,每一个季度导致DRAM市场下跌至少41%。

图注:2022年6月DRAM销售额下降。图片来源: IC Insights

趋势1:突破传统架构,RRAM(ReRAM)存算一体有望提升计算系统能效比

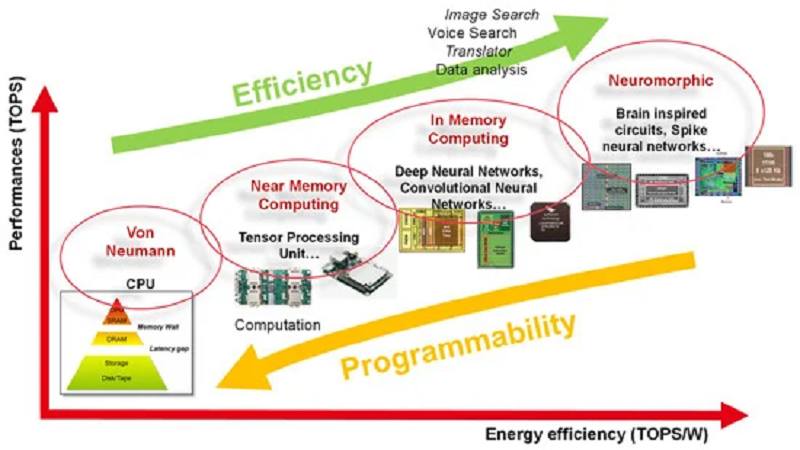

文章开头提及,开发新计算系统源于几点:数据指数增长、功耗增加,当前计算系统的性能限制也是原因之一。对此,业界提出“近内存”或存内计算(In-memory Computing),以解决数据中心的几个问题,包括数据传输“存储墙”(Memory barrier)、高功耗和时间成本。涉及深度学习网络的数据中心需要巨大的计算能量,要求高可靠性、更出色容量、带宽和性能的存储器,从而衍生出关于新的非冯·诺依曼系统的新兴存储技术研究。

图注:几种计算系统架构的性能和能效对比。图片来源:mdpi.com

普遍认为,RRAM(也即ReRAM,阻变式随机存取存储器)、PCM(相变随机存取存储器)和MRAM(磁随机存取存储器)等是下一代存储技术路线,这些也是“存内计算”的基础技术,从技术特征来看,这些技术有哪些独特性?

资深电子器件专家Ray表示,上述的下一代非易失性存储器首先是作为存储级内存被提出的,在存储层级中介于

内存和硬盘之间,因此,存储的性能指标对这些下一代非易失性存储器仍然适用,如面积、功耗、读写速度、集成性、成本等。此外,下一代非易失性存储器也非常适用于存内计算,而存内计算又对这些存储器提出了新的要求,如开关比、多阻态、鲁棒性等。RRAM、PCM和MRAM等是目前研究较多的下一代非易失性存储器,它们各有优势和不足。

MRAM中的磁性材料磁化方向变化的时候,从磁性材料两端电极上读取得到的隧穿电流会发生变化,从而得到不同电阻,其编写速度快、重复编写周期长,但其材料制备较复杂、开关比较低、易受扰动。

PCM是利用相变材料在焦耳热作用下,在结晶态和非晶态之间转换,从而呈现出不同阻态,其已经在英特尔等公司的产品中使用,大规模集成性较好,但其写入速度较慢、写入能耗较大。

RRAM主要依靠绝缘层在电场作用下,通过离子的迁移形成导电细丝,再通过控制导电细丝的通断控制阻态,综合来看在各个指标上均具有比较优异的性质,其结构简单、存储密度高且支持片上3D集成、开关比可达1000以上、读写速度和功耗适中,且其可通过控制导电细丝的形态形成多阻态,从而模仿生物大脑中神经突触功能,适合存内计算和类脑计算。

目前RRAM作为新兴存储器,其规模化制备的良率、成本、外围控制电路等还需进一步优化,同时,我们也很欣喜地看到国内和国际的多家制造厂商已经布局RRAM的制备,并且已完成晶圆级RRAM芯片的流片。

在RRAM商业化之前,还需要解决哪些难题?Ray说道,同其他研究一样,RRAM的科研主要解决科学问题,在进行商业化的时候还有很多工程问题需要解决,包括大规模制造、架构和软件的配合、应用场景等,但目前来看,其很多科学问题已经经过了大量的研究,取得了很多突破,这些技术问题相信随着时间的推移也将逐步解决。

物联网和网络边缘的人工智能(AI)和机器学习(ML)快速增长,这些应用端的计算系统的能效比的问题日益突出,而RRAM作为一种较佳的解决方案,成为研究的焦点。

Ray进一步说道,目前的计算架构采用冯诺伊曼架构,其存储与计算单元分离,因此,在AI等计算应用中,大量数据需要不断在片下的内存和片上的计算单元之间搬运,然而由于内存带宽不足带来的“存储墙”问题,导致计算延时和能耗较高,难以满足AI模型的算力和功耗需求。存算一体技术将存储单元与计算单元融合,在存储器内利用物理定律进行计算,避免了“存储墙”问题,极大地降低了数据搬运的能耗和延时,并提升了计算的能效比。基于RRAM的存算一体目前是国内外的研究热点和前沿,其主要实现方式分为两种,即模拟式存算一体和数字式存算一体。

模拟式存算一体利用了RRAM的模拟式阻态特性,通过电导存储多比特数据。以神经网络中应用较广泛的矩阵乘积运算为例,其电导值存储神经网络的权值,输入为电压值,利用欧姆定律完成乘法,得到电流值,然后阵列中同一条数据线上的电流根据基尔霍夫电流定律相加,从而完成乘加运算。模拟式存算一体可以达到较高的存储密度,但

其对环境噪声和温度较敏感,运算精度较低,主要适合低精度、小算力的应用场景。

而数字式存算一体中,其每个RRAM只存储一比特数据,经过乘法运算得到电流后再经过数字电路进行后续加法等运算,此种方法虽然存储密度低于模拟式存算一体,但其优势是在保证计算能效比的前提下,支持高精度、大算力的运算,提高计算的鲁棒性,从而极大地拓展了存算一体的应用场景。

相比于CMOS器件,目前RRAM的局限性主要体现在编写周期有限上,因此目前RRAM主要适用于AI推理等操作,而相信随着工艺的演进,得到更高编写周期的RRAM也是非常有希望的。另一个局限性是RRAM阻值的波动性,而此问题在数字式存算一体中可以得到很好的解决。

趋势2:CXL或将突破DRAM在服务器的限制

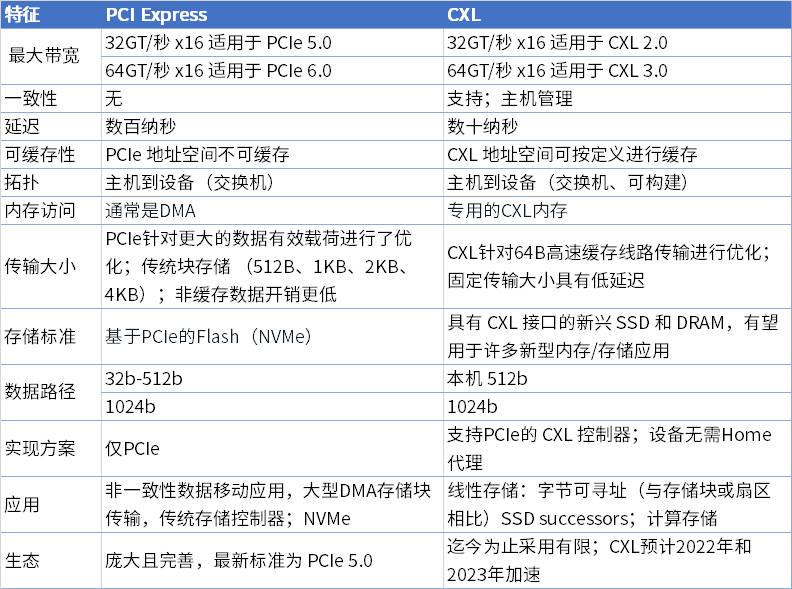

为满足新兴数据密集型应用的需求,内存大小必须增加,内存和CPU之间的带宽也必须增加,因此,处理器内存接口迅速发展,也就出现了新的开放接口和协议,包括CXL(Compute Express Link)、GenZ和OpenCAPI等,随着CXL收购了Gen Z和OpenCAPI资产,该领域的标准主要是PCIe和CXL。

CXL能够整合各种xPU之间的性能,进而优化AI与HPC所需要的硬件成本,并突破原先的硬件限制。而该规格可先实现的产品则是CXL存储器扩充(CXL Memory Expander),TrendForce认为,在各种CXL相关产品内,CXL存储器扩充将成为前驱产品,并与DRAM最为相关。目前存储器厂正聚焦CXL存储器扩充器产品,以突破AI/ML服务器DRAM硬件限制。目前原厂开发的CXL存储器扩充器使用的是DDR5,不过现阶段仍受PCIe 5.0接口速度局限,释出速度仅略等同于DDR4。未来一旦CPU支援到PCIe 6.0亦或是更高的规格,则足以使DDR5发挥完整的速度。以CXL存储器扩充器结构来看,除了DRAM外,需搭配一颗CXL控制器((CXL controller)),其受益厂商包括Montage、Marvell与Microchip等。

虽然以64GT/s的速度引入PCIe6.0.1有助于增加存储的可用带宽,对延迟的影响微乎其微,但缺乏一致性,这样就限制了PCIe的应用,比如SSD,使用PCIe作为传输接口的NVMe已经成为SSD的主要组件,因此,业界正在开发支持CXL接口的下一代SSD。

图注:PCIe与CXL在存储应用中的对比。图片来源:Synopsys

趋势3:新一代DRAM初具规模,200多层NAND Flash开发加速

企业数字化转型的加速,数据中心提升了服务器出货量,也促进新型DRAM内存模块应用。服务器RDIMM插槽数量有限,使用CXL使设备在执行高速计算时能够避免插槽数量的限制,同时增加系统可使用的DRAM数量。到2023年,主流服务器CPU将支持CXL 1.0,而且DRAM模块也将采用DDR5。为了有效运行人工智能和机器学习,服务器GPU将引入新一代HBM3规范,部分内存制造商和xPU提供商已经开始规划新一代内存,有望在2023年获得市场份额。就NAND Flash而言,堆叠层的数量将增加,预计四家供应商将转向200层以上的NAND Flash。在SSD传输接口方面,企业SSD将进一步支持PCIe 5.0传输,传输速率大幅提高到32GT/s,用于高速计算需求,也有助于企业SSD平均容量快速提升。

小结

承载人工智能和机器学习工作负荷的计算系统需求增加,数据中心内存和存储的增长将超过一般半导体市场,驱使新型计算系统崭露头角。RRAM存算一体、CXL、DDR5等目前看来是计算系统性能提升的优选技术,带动存储器革新,尽管存储器行情预期不佳,技术革新仍然以自己的节奏前进。

全部评论